# RCA MOS FIELD-EFFECT TRANSISTOR

For Critical Chopper Applications & Multiplex Service

3N138

File No. 283

RCA-3N138‡ is a silicon, insulated-gate field-effect transistor of the N-channel depletion type, utilizing the MOS\* construction. It is intended primarily for critical chopper and multiplex applications up to 60MHz.

This transistor features a New Terminal Arrangement in which the gate and source connections are interchanged to provide maximum isolation between the output (drain) and the input (gate) terminals. Although this new basing configuration does not appreciably change the measured device feedback capacitance, it permits the use of external interterminal shields to reduce the feedback due to external capacitances, particularly on printed circuit boards. This feature makes it possible to minimize feedthrough capacitance.

The insulated gate provides a very high value of input resistance (10<sup>14</sup> ohms typ.), which is relatively insensitive to temperature and is independent of gate-bias conditions (positive, negative, or zero bias). The 3N138 also features extremely low feed-through capacitance (0.18pF typ.) and zero inherent offset voltage.

The 3N138 is hermetically sealed in the JEDEC TO-72 package and features a gate metallization that covers the entire source-to-drain channel.

‡ Formerly Dev. No. TA7032. \* Metal-Oxide-Semiconductor.

## Maximum Ratings, Absolute-Maximum Values:

| (Substrate connected to source unless otherwise speci                                                                     | fied)                  |

|---------------------------------------------------------------------------------------------------------------------------|------------------------|

| DRAIN-TO-SOURCE<br>VOLTAGE, V <sub>DS</sub> +35 max.                                                                      | v                      |

| $\begin{array}{ccc} DRAIN-TO-SUBSTRATE \\ VOLTAGE, \ V_{DB} & +35, -0.3 \ max. \end{array}$                               | v                      |

|                                                                                                                           | v                      |

|                                                                                                                           | v                      |

| $\begin{array}{ccc} \textbf{PEAK GATE-TO-SOURCE} \\ \textbf{VOLTAGE, V}_{\textbf{GS}} & & \pm 14~\text{max.} \end{array}$ | v                      |

| PEAK VOLTAGE, GATE-TO-ALL OTHER TERMINALS: $V_{GS}$ , $V_{GD}$ , $V_{GB}$ , non-repetitive $\pm 45$ max.                  | v                      |

| DRAIN CURRENT, $I_D$ (Pulse duration 20 ms, duty factor $\leq 0.10$ ) 50 max.                                             | mA                     |

| TRANSISTOR DISSIPATION, P <sub>T</sub> : At ambient temperatures from -65 to +125°C                                       | $\mathbf{m}\mathbf{W}$ |

| AMBIENT TEMPERATURE         RANGE:         Storage       -65 to +150         Operating       -65 to +125                  | °C<br>°C               |

| LEAD TEMPERATURE (During Soldering): At distances $\geq 1/32''$ to seating sur-                                           |                        |

| face for 10 seconds max. 265 max.                                                                                         | $^{\circ}\mathrm{C}$   |

# SILICON INSULATED-GATE FIELD-EFFECT TRANSISTOR N-Channel Depletion Type

JEDEC

For Critical Chopper Applications and Multiplex Service up to 60 MHz:

in Military Communications, Navigation, and Instrumentation Equipment in Industrial Instrumentation and Control Circuits

# **Applications**

- Servo Amplifiers

- Telemetry Amplifiers

- Computer Operational Amplifiers

- Sampling Circuits

- Electrometer Amplifiers

#### **Features**

new terminal arrangement

- 1 Drain

- 2 Source

- 3 Insulated Gate

- 4 Bulk (Substrate) and Case

- excellent thermal stability

- zero inherent offset voltage

- low leakage current: 10 pÅ max.

- low "on" resistance —

$r_{\rm DS}({

m on}) = 240\Omega \ {

m typ.} \ ({

m V}_{\rm GS} = {

m OV})$

high "off" resistance —

$R_{\rm DS}({\rm off}) = 10^{10}\Omega$  typ.

low feedback capacitance —

$C_{rss} = 0.18pF$  typ.

• low input capacitance —

$C_{iss} = 3pF typ.$

symmetrical configuration —

permits interchangeability of drain and source

Information furnished by RCA is believed to be accurate and reliable. However, no responsibility is assumed by RCA for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of RCA.

ELECTRICAL CHARACTERISTICS, at  $T_A=25^\circ$  C, Unless Otherwise Specified. Substrate Connected to Source.

| CHARACTERISTICS                                              | SYMBOLS                     | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                   |                     | UNITS             |            |          |

|--------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------|------------|----------|

|                                                              |                             |                                                                                                                                                                                                                                                                                                                                                                   | Min.                | Тур.              | Max.       |          |

| Gate-Leakage Current                                         | $I_{\mathrm{GSS}}$          | $\begin{array}{l} {\rm V_{GS}=\pm10,V_{\rm DS}=0,T_{\rm A}=25^{\circ}\textrm{C}} \\ {\rm V_{GS}=\pm10,V_{\rm DS}=0,T_{\rm A}=125^{\circ}\textrm{C}} \end{array}$                                                                                                                                                                                                  |                     | 0.1<br>20         | 10<br>200  | pA<br>pA |

| Drain-to-Source "ON" Resistance                              | r <sub>DS</sub> (on)        | $\begin{array}{c} \text{V}_{\rm GS} = \text{ 0, V}_{\rm DS} = \text{ 0, f} = \text{ 1 KHz, T}_{\rm A} = 25^{\circ}\text{C} \\ \text{V}_{\rm GS} = +10, \text{V}_{\rm DS} = \text{ 0, f} = \text{ 1 KHz, T}_{\rm A} = 25^{\circ}\text{C} \\ \text{V}_{\rm GS} = \text{ 0, V}_{\rm DS} = \text{ 0, f} = \text{ 1 KHz, T}_{\rm A} = 125^{\circ}\text{C} \end{array}$ |                     | 240<br>135<br>350 | 300        | Ω<br>Ω   |

| Drain-to-Source "OFF" Resistance                             | R <sub>DS</sub> (off)       | $V_{GS} = -10, V_{DS} = +1$                                                                                                                                                                                                                                                                                                                                       | 2 × 10 <sup>8</sup> | 1010              |            | Ω        |

| Drain-to-Source Cutoff Current                               | I <sub>D</sub> (off)        | $egin{array}{lll} V_{\mathrm{GS}} = -10, V_{\mathrm{DS}} = +1, T_{\mathrm{A}} = 25^{\circ}\mathrm{C} \\ V_{\mathrm{GS}} = -10, V_{\mathrm{DS}} = +1, T_{\mathrm{A}} = 125^{\circ}\mathrm{C} \end{array}$                                                                                                                                                          | _                   | 0.01<br>0.01      | 0.5<br>0.5 | nΑ<br>μΑ |

| Small-Signal, Short-Circuit, Reverse<br>Transfer Capacitance | $\mathtt{C}_{\mathrm{rss}}$ | $V_{\rm GS} = -10, V_{\rm DS} = 0, f = 1 \mbox{ MHz}$                                                                                                                                                                                                                                                                                                             | _                   | 0.18              | 0.25       | pF       |

| Small-Signal, Short-Circuit, Input<br>Capacitance            | $C_{iss}$                   | $V_{\mathrm{GS}} = -10$ , $V_{\mathrm{DS}} = 0$ , $f = 1$ MHz                                                                                                                                                                                                                                                                                                     | -                   | 3                 | 5          | pF       |

| Zero-Gate-Bias Forward Transconductance                      | g <sub>fs</sub>             | $V_{\rm GS} = 0, V_{\rm DS} = 12$                                                                                                                                                                                                                                                                                                                                 | _                   | 6000              | _          | μmho     |

| Offset Voltage                                               | V <sub>0</sub>              | $V_{\mathrm{GS}} = \pm 10, V_{\mathrm{DS}} = 0$                                                                                                                                                                                                                                                                                                                   |                     | 0*                |            | ٧        |

<sup>\*</sup> In measurements of Offset Voltage, thermocouple effects and contact potentials in the measurement setup may cause erroneous readings of 1 microvolt or more. These errors may be minimized by the use of solder having a low thermal e.m.f., such as Leeds & Northrup No. 107-1.0.1, or-equivalent.

## **OPERATING CONSIDERATIONS**

The flexible leads of the 3N138 are usually soldered to the circuit elements. As in the case of any high-frequency semiconductor device, the tips of soldering irons should be grounded, and appropriate precautions should be taken to protect the device against high electric fields.

This device should not be connected into or disconnected from circuits with the power on because high transient voltages may cause permanent damage to the device.

SUNGA

# TYPICAL CHARACTERISTICS

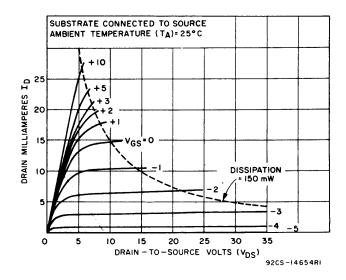

Fig. 1 - Drain Current vs Drain-to-Source Voltage

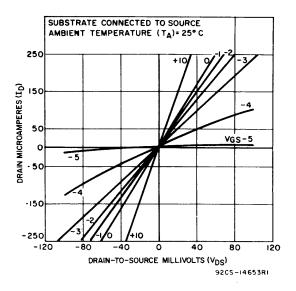

Fig. 2 – Low-Level Drain Current vs Drain-to-Source Voltage

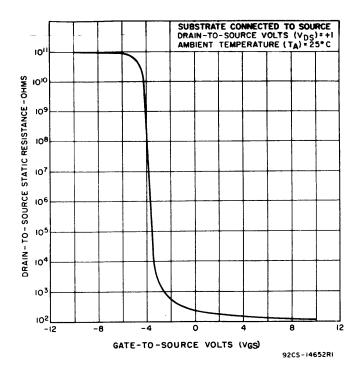

Fig. 3 — Drain-to-Source Static Resistance vs Gate-to-Source Voltage

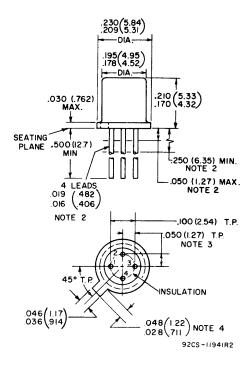

# DIMENSIONAL OUTLINE JEDEC TO-72

## Dimensions in inches and millimeters

Note 1: Dimensions in parentheses are in millimeters and are derived from the basic inch dimensions as indicated.

Note 2 The specified lead diameter applies in the zone between 0.050" (1.27 mm) and 0.250" (6.35 mm) from the seating plane. From 0.250" (6.35 mm) to the end of the lead a maximum diameter of 0.021" (0.533 mm) is held. Outside of these zones, the lead diameter is not controlled.

Note 3: Leads having a maximum diameter of 0.019" (0.482 mm) at a gauging plane of 0.054" (1.372 mm) + 0.001" (0.925 mm) - 0.000" (0.000 mm) below seating plane shall be within 0.007" (0.177 mm) of their true position (location) relative to a maximum width of tab.

Note 4: Measured from actual maximum diameter.

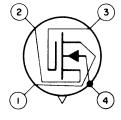

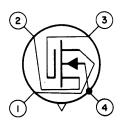

# TERMINAL DIAGRAM

- 1 Drain

- 2 Source

- 3 Insulated Gate

- 4 Bulk (Substrate) and Case

# RCA MOS FIELD-EFFECT TRANSISTOR

For Industrial and Military Applications to 175 MHz

3N142

File No 286

RCA-3N142† is a silicon, insulated-gate field-effect transistor of the N-channel depletion type utilizing the MOS\* construction. It features

- high input resistance 1000 megohms

- low feedback capacitance 0.2pF max.

- low noise figure 4dB typ.

- high useful power gain —

neutralized 17dB typ.

at 100MHz

unneutralized 14dB typ.

- hermetically sealed TO-104 metal package

RCA-3N142 is intended primarily for use as the rf amplifier in FM receivers covering the 88 to 108MHz band, but can be used for general amplifier applications at frequencies up to 175 MHz.

The wide dynamic range of the 3N142 reduces cross-modulation effects in AM receivers and minimizes the generation of spurious responses in FM receivers.

#### Maximum Ratings, Absolute-Maximum Values:

| DRAIN-TO-SOURCE<br>VOLTAGE, V <sub>DS</sub>       | +20 max. V                                                                             |

|---------------------------------------------------|----------------------------------------------------------------------------------------|

| GATE-TO-SOURCE                                    |                                                                                        |

| VOLTAGE, V <sub>GS</sub> :                        |                                                                                        |

| Continuous                                        | 0 to -8 max. V                                                                         |

| Instantaneous                                     | $\pm$ 15 max. V                                                                        |

| DRAIN-TO-GATE                                     |                                                                                        |

| VOLTAGE, V <sub>DG</sub>                          | +20 max. V                                                                             |

| DRAIN CURRENT, ID**                               | 50 max. mA                                                                             |

| TRANSISTOR DISSIPATION, PT:                       |                                                                                        |

| At ambient   up to 85°C temperatures   above 85°C | $\begin{array}{ccc} 100 \; max. & mW \\ Derate \; at \; 6.67 mW/^{\circ}C \end{array}$ |

| AMBIENT TEMPERATURE.                              |                                                                                        |

|                                                   |                                                                                        |

| Storage                                           |                                                                                        |

| Operating                                         | -65 to +100 °C                                                                         |

| LEAD TEMPERATURE                                  |                                                                                        |

| (During Soldering):                               |                                                                                        |

| At distances ≥ 1/32" from seating                 |                                                                                        |

<sup>\*\*</sup> Pulse Value. Pulse duration, 20ms max., Duty factor ≤0.1

surface for 10 seconds max. 265 max.

# SILICON INSULATED-GATE FIELD-EFFECT TRANSISTOR N-Channel Depletion Type

JEDEC

For Frequencies up to 175 MHz

## **Applications**

- RF Amplifier, Mixer, and Oscillator in: CB and Mobile Communication Receivers Aircraft and Marine Receivers CATV and MATV Equipment

- Industrial Control Circuits

- Variable Attenuators

- Current Limiters

- Instrumentation Equipment

- High-Impedance Timing Circuits

## **Performance Features**

- large dynamic range

- enhanced signal-handling capability for low crossmodulation

- dual-polarity gate permits positive and negative swing without degradation of input impedance

- reduced spurious responses in FM receivers

- permits use of vacuum-tube biasing techniques

- excellent thermal stability for critical oscillator designs

Information furnished by RCA is believed to be accurate and reliable. However, no responsibility is assumed by RCA for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of RCA.

<sup>†</sup> Formerly Dev. No. TA7306

<sup>\*</sup> Metal-Oxide-Semiconductor

ELECTRICAL CHARACTERISTICS, at  $T_{\rm A}=25^{\circ}$  C Unless Otherwise Specified. Bulk (Substrate) Connected to Source

|                                                                                |                       | TEST CONDITIONS      |                                                         |                                                        |                                          |      | LIMITS        |      |       |

|--------------------------------------------------------------------------------|-----------------------|----------------------|---------------------------------------------------------|--------------------------------------------------------|------------------------------------------|------|---------------|------|-------|

| CHARACTERISTICS                                                                | SYMBOLS               | FREQUENCY<br>f       | DC<br>DRAIN-TO-<br>SOURCE<br>VOLTAGE<br>V <sub>DS</sub> | DC<br>GATE-TO-<br>SOURCE<br>VOLTAGE<br>V <sub>GS</sub> | DC<br>DRAIN<br>CURRENT<br>I <sub>D</sub> |      | TYPE<br>3N142 |      | UNITS |

|                                                                                |                       | MHz                  | V                                                       | ٧                                                      | mA                                       | Min. | Тур.          | Max. |       |

| Drain-to-Source Cutoff Current                                                 | I <sub>D</sub> (off)  |                      | 20                                                      | -8                                                     |                                          | _    | _             | 100  | μΑ    |

| Zero-Bias Drain Current*                                                       | I <sub>DSS</sub>      |                      | 15                                                      | 0                                                      |                                          | 5    | 20            | 50   | mA    |

| Gate Reverse Current                                                           | I <sub>GSS</sub>      | $T_A = 25^{\circ}C$  | 0                                                       | -8                                                     |                                          | _    |               | 1    | nA    |

|                                                                                |                       | $T_A = 100^{\circ}C$ | 0                                                       | -8                                                     |                                          | _    | _             | 100  | nA    |

| Gate-to-Source Cutoff Voltage                                                  | V <sub>G</sub> s(off) |                      | 20                                                      |                                                        | 0.05                                     | -2   | -5            | -8   | V     |

| Small-Signal, Short-Circuit<br>Reverse-Transfer Capacitance<br>(Drain-to-Gate) | C <sub>rss</sub>      | 1                    | 15                                                      |                                                        | 5                                        |      | 0.12          | 0.2  | pF    |

| Input Resistance                                                               | $f_{\mathrm{is}}$     | 100                  | 15                                                      |                                                        | 5.                                       | 2    | 4.5           |      | KΩ    |

| Input Capacitance                                                              | C <sub>iss</sub>      | 1                    | 15                                                      |                                                        | 5                                        |      | 5.5           | 10   | pF    |

| Output Resistance                                                              | r <sub>os</sub>       | 100                  | 15                                                      |                                                        | 5                                        | 2.25 | 4.2           | _    | ΚΩ    |

| Output Capacitance                                                             | Coss                  | 100                  | 15                                                      |                                                        | 5                                        |      | 1.4           | _    | pF    |

| Forward Transconductance                                                       | grs                   | 100                  | 15                                                      |                                                        | 5                                        | 4    | 7.5           | _    | mmho  |

| Maximum Available Power Gain                                                   | MAG                   | 100                  | 15                                                      |                                                        | 5                                        |      | 24            | -    | dB    |

| Maximum Usable Power Gain<br>(Unneutralized)                                   | MUG                   | 100                  | 15                                                      |                                                        | 5                                        |      | 14            | _    | dB    |

| Maximum Usable Power Gain<br>(Neutralized)                                     | MUG                   | 100                  | 15                                                      |                                                        | 5                                        | 15   | 17            | _    | dB    |

| Noise Figure                                                                   | NF                    | 100                  | 15                                                      |                                                        | 5                                        | -    | 4             | 5    | dB    |

<sup>\*</sup> Pulse test: Pulse Duration 20 ms max. Duty Factor  $\leq$  0.15.

# **OPERATING CONSIDERATIONS**

The flexible leads of the 3N142 are usually soldered to the circuit elements. As in the case of any high-frequency semiconductor device, the tips of soldering irons should be grounded, and appropriate precautions should be taken to protect the device against high electric fields.

This device should not be connected into, or disconnected from, circuits with the power on because high transient voltages may cause permanent damage to the device.

# TYPICAL CHARACTERISTICS

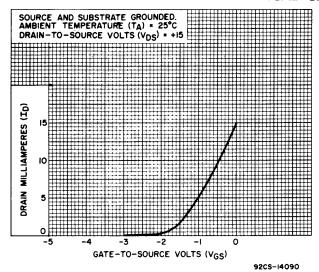

Fig. 1 – Typical Characteristic of Drain Current ( $I_D$ ) vs Gate-to-Source Voltage ( $V_{\rm GS}$ )

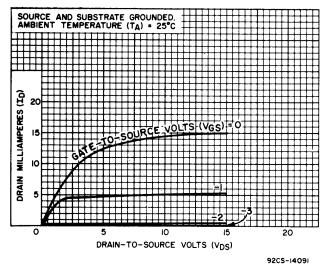

Fig. 2 - Drain Current ( $I_D$ ) vs Drain-to-Source Voltage ( $V_{D8}$ )

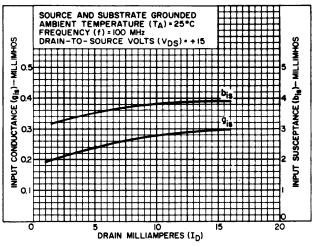

# TYPICAL y PARAMETER CHARACTERISTICS

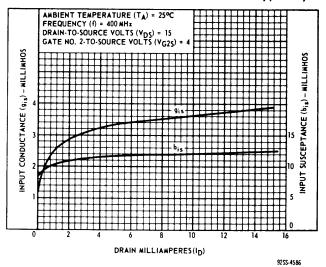

Fig. 3 – Input Admittance  $(y_{is})$  vs Drain Current  $(I_D)$

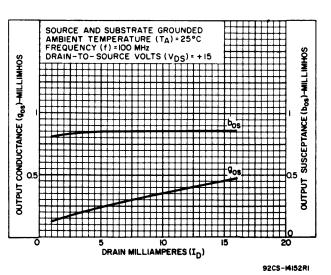

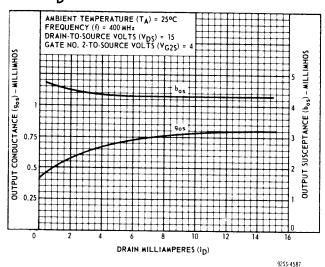

Fig. 5 – Output Admittance  $(y_{os})$  vs Drain Current  $(I_D)$

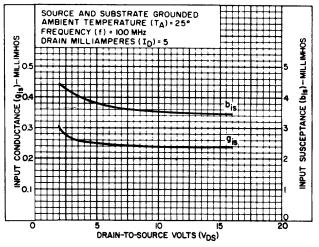

Fig. 4 — Input Admittance  $(y_{is})$  vs Drain-to-Source Voltage  $(V_{DS})$

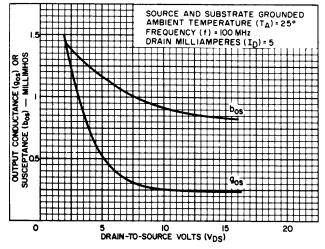

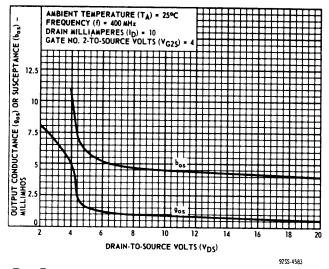

Fig. 6 – Output Admittance  $(y_{os})$  vs Drain-to-Source Voltage  $(V_{DS})$

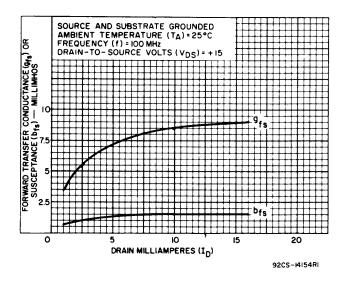

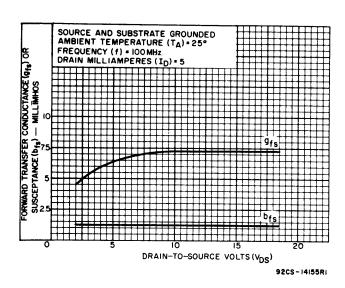

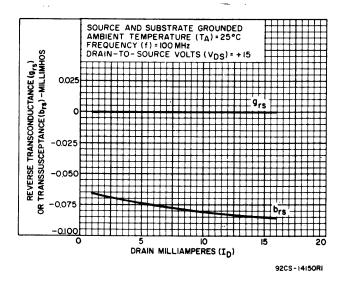

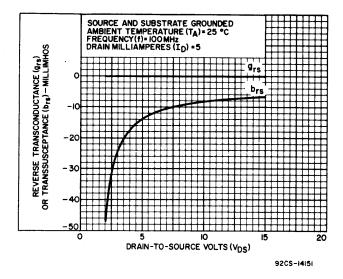

# TYPICAL y PARAMETER CHARACTERISTICS

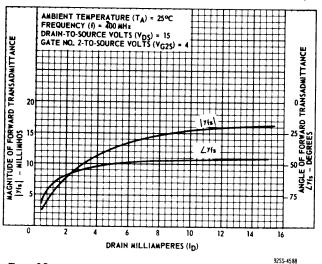

Fig. 7 – Forward Transadmittance  $(y_{fs})$  vs Drain Current  $(I_D)$

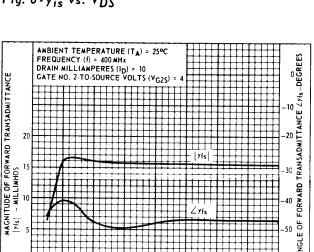

Fig. 8 — Forward Transadmittance  $(y_{fs})$  vs Drain-to-Source Voltage  $(V_{DS})$

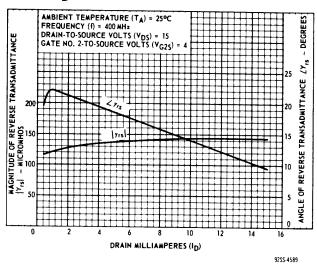

Fig. 9 – Reverse Transadmittance  $(y_{rs})$  vs Drain Current  $(I_D)$

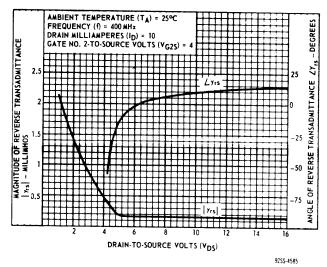

Fig. 10 – Reverse Transadmittance  $(y_{rs})$  vs Drain-to-Source Voltage  $(V_{DS})$

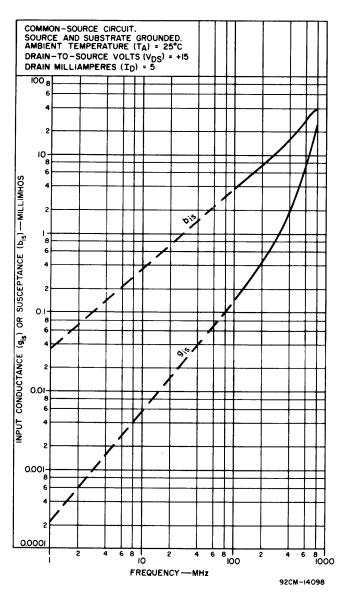

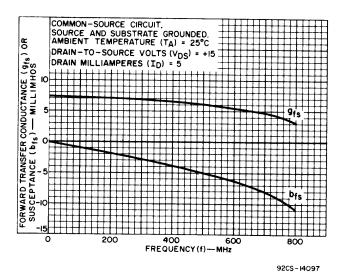

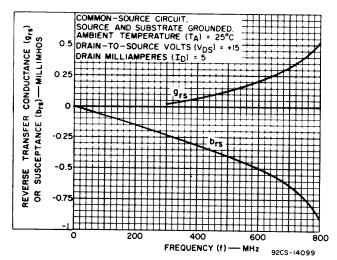

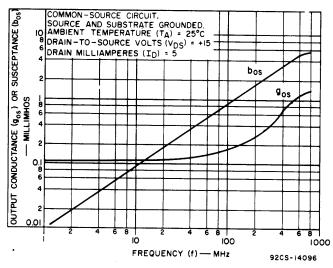

# TYPICAL COMMON-SOURCE ADMITTANCE (Y) COMPONENTS vs FREQUENCY

Fig. 11 - Input Admittance (Yis) Components

Fig. 12 - Forward Transadmittance ( $Y_{fs}$ ) Components

Fig. 13 - Reverse Transadmittance (Y<sub>rs</sub>) Components

Fig. 14 - Output Admittance (Yos) Components

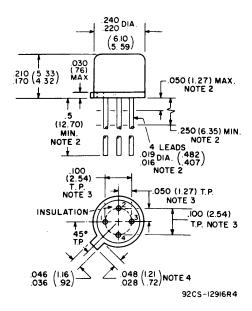

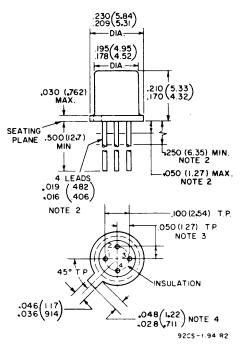

# DIMENSIONAL OUTLINE TO-104

#### DIMENSIONS IN INCHES AND MILLIMETERS

Note 1: Dimensions in parentheses are in millimeters and are derived from the basic inch dimensions as indicated.

Note 2: The specified lead diameter applies in the zone between 0.050 " (1.27 mm) and 0.250 "(6.35 mm) from the seating plane. From 0.250 "(6.35 mm) to the end of the lead a maximum diameter of 0.021 "(0.533 mm) is held. Outside of these zones, the lead diameter is not controlled.

**Note 3:** Leadshaving a maximum diameter of 0.019 " (0.482 mm) at a gauging plane of 0.054 " (1.372 mm) + 0.001 " (0.025 mm) -0.000 " (0.000 mm) below seating plane shall be within 0.007" (0.177 mm) of their true position (location) relative to a maximidth of tab.

Note 4: Measured from actual maximum diameter.

#### TERMINAL DIAGRAM

LEAD 1 - DRAIN

LEAD 2 - SOURCE

LEAD 3 - INSULATED GATE

LEAD 4 - BULK (SUBSTRATE) AND CASE

# MOS Field-Effect Transistors

**N-Channel Depletion Types**

**3N200**

# Silicon Dual Insulated-Gate Field-Effect Transistor

With Integrated Gate-Protection Circuits

For Military and Industrial Applications up to 500 MHz

## **Applications**

- RF amplifier, mixer, and IF amplifier in military and industrial communications equipment

- Aircraft and marine vehicular receivers

- CATV and MATV equipment

- Telemetry and multiplex equipment

RCA-3N200 $^{\bullet}$  is an n-channel silicon, depletion type, dual insulated-gate field-effect transistor.

Special back-to-back diodes are diffused directly into the MOS<sup>A</sup> pellet and are electrically connected between each insulated gate and the FET's source. The diodes effectively bypass any voltage transients which exceed approximately ±10 volts. This protects the gates against damage in all normal handling and usage.

A feature of the back-to-back diode configuration is that it allows the 3N200 to retain the wide input signal dynamic range inherent in the MOSFET. In addition, the low junction capacitance of these diodes adds little to the total capacitance shunting the signal gate.

The excellent overall performance characteristics of the RCA-3N200 make it useful for a wide variety of rf-amplifier

Maximum Ratings, Absolute-Maximum Values, at TA = 250C DRAIN-TO-SOURCE VOLTAGE, VDS . . . . -0.2 to +20 GATE No.1-TO-SOURCE VOLTAGE, VG1S: -6 to +3 Peak ac -6 to +6 GATE No.2-TO-SOURCE VOLTAGE, VG2S Continuous (dc)..... -6 to 30% of V<sub>DS</sub> Peak ac -6 to +6 \* DRAIN-TO-GATE VOLTAGE, V<sub>DG1</sub> OR V<sub>DG2</sub> ..... +20 50 mΑ up to 25°C 330 mW At ambient At ambient | up to 25°C ..... temperatures | above 25°C ..... derate linearly at 2.2 mW/OC \* AMBIENT TEMPERATURE RANGE: -65 to +175 seating surface for 10 seconds max.

\*In accordance with JEDEC registration data format (JS-9 RDF-19A)

applications at frequencies up to 500 MHz. The two serially-connected channels with independent control gates make possible a greater dynamic range and lower cross-modulation than is normally achieved using devices having only a single control element.

The two-gate arrangement of the 3N200 also makes possible a desirable reduction in feedback capacitance by operating in the common-source configuration and ac-grounding Gate No. 2. The reduced capacitance allows operation at maximum gain without neutralization; and, of special importance in rf-amplifiers, it reduces local oscillator feedthrough to the antenna.

The 3N200 is hermetically sealed in the metal JEDEC TO-72 package.

- ▲ Metal-Oxide-Semiconductor.

- ♦ Formerly developmental type TA7684

#### Performance Features

- Superior cross-modulation performance and greater dynamic range than bipolar or single-gate FET s

- Wide dynamic range permits large-signal handling before overload

- Dual-gate permits simplified agc circuitry

- Virtually no agc power required

- Greatly reduces spurious responses in FM receivers

#### Device Features

- Back-to-back diodes protect each gate against handling and in-circuit transients

- High forward transconductance —

- $g_{fS} = 15,000 \mu mho (typ.)$

- High unneutralized RF power gain —

G<sub>ps</sub> = 12.5 dB (typ.) at 400 MHz

= 19 dB (typ.) at 200 MHz

- Low VHF noise figure 4.5 dB (typ.) at 400 MHz

3.0 dB (typ.) at 200 MHz

|      | ELECTRICAL CHARACTERISTICS                                                      |             |                        | TEST COMPLETIONS                                                             |                                                                                         |                                          | LIMITS |        |         |          |

|------|---------------------------------------------------------------------------------|-------------|------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------|--------|--------|---------|----------|

|      | nt T <sub>A</sub> = 25°C<br>Intess otherwise spec                               | ified       | SYMBOLS                | TEST CONDITIONS                                                              |                                                                                         |                                          | Min.   | Тур.   | Max.    | UNITS    |

| •[   | Gate No. 1-to-Source Cuto                                                       | f Voltage   | V <sub>G1S(off)</sub>  |                                                                              | $V_{DS} = +15 \text{ V}, I_D = 50 \mu \text{ A}$<br>$V_{G2S} = +4 \text{ V}$            |                                          |        | -1     | -3      | ٧        |

| •    | Gate No. 2-to-Source Cuto                                                       | f Voltage   | V <sub>G2S(off)</sub>  | V <sub>DS</sub> = +1<br>V <sub>G1S</sub> = 0                                 | 5 V, I <sub>[</sub>                                                                     | <sub>)</sub> = 50 μ A                    | -0.1   | -1     | -3      | ٧        |

| •[   | Gate No. 1-Terminal Forw                                                        | ard Current | I <sub>G1SSF</sub>     | V <sub>G1S</sub> = +<br>V <sub>G2S</sub> = V                                 | 1 <b>V</b><br>DS = 0                                                                    | $T_A = 25^{\circ}C$ $T_A = 100^{\circ}C$ | -      | -      | 50<br>5 | nΑ<br>μΑ |

| • [  | Gate No. 1-Terminal Reve                                                        | rse Current | I <sub>G1SSR</sub>     |                                                                              |                                                                                         | $T_A = 25^{\circ}C$ $T_A = 100^{\circ}C$ | -      | -      | 50<br>5 | nΑ<br>μΑ |

| •    | Gate No. 2-Terminal Forward Current I <sub>G2SSF</sub>                          |             | <sup>I</sup> G2SSF     | V <sub>G2S</sub> = +                                                         | V <sub>G2S</sub> = +6 V<br>V <sub>G1S</sub> = V <sub>DS</sub> = 0 T <sub>A</sub> = 25°C |                                          | -      | -      | 50<br>5 | nA<br>μA |

| .[   | Gate No. 2-Terminal Reverse Current                                             |             | I <sub>G2SSR</sub>     | V <sub>G2S</sub> = -6 V T <sub>A</sub>                                       |                                                                                         |                                          |        | -      | 50<br>5 | nA<br>μA |

| , 7  | Zero-Bias Drain Current                                                         |             | l <sub>DS</sub>        | V <sub>DS</sub> = +15 V, V <sub>G1S</sub> = 0<br>V <sub>G2S</sub> = +4 V     |                                                                                         |                                          | 0.5    | 5.0    | 12      | mA       |

|      | Forward Transconductance (Gate No. 1-to-Drain) 8fs                              |             | gfs                    | f = 1kHz                                                                     |                                                                                         | 10,000                                   | 15,000 | 20,000 | μmho    |          |

| S    | mall-Signal, Short-Circuit<br>Capacitance                                       | Input       | C <sub>iss</sub>       | V <sub>DS</sub> = +15 V<br>I <sub>D</sub> = 10 mA<br>V <sub>G2S</sub> = +4 V |                                                                                         |                                          | 4.0    | 6.0    | 8.5     | pF       |

| F    | mall-Signal, Short-Circuit<br>Reverse Transfer Capacita<br>Drain-to-Gate-No. 1) |             | C <sub>rss</sub>       |                                                                              |                                                                                         | f = 1 MHz                                | 0.005  | 0.02   | 0.03    | pF       |

|      | mall-Signal, Short-Circuit<br>Capacitance                                       | Output      | Coss                   |                                                                              |                                                                                         |                                          | -      | 2.0    | -       | pF       |

| · [P | ower Gain (see Fig. 1)                                                          |             | GPS                    |                                                                              |                                                                                         |                                          | 10     | 12.5   | -       | dВ       |

| N    | Noise Figure (see Fig. 1)                                                       |             | NF                     | ]                                                                            |                                                                                         | f = 400 MHz                              | -      | 4.5    | 6.0     | dB       |

| B    | Bandwidth                                                                       |             | BW                     |                                                                              |                                                                                         |                                          | 28     | -      | 38      | MHz      |

|      | iate-to-Source Forward<br>Breakdown Voltage                                     | Gate No. 1  | V <sub>(BR)G1SSF</sub> | G1SSF =   VG2                                                                |                                                                                         | s = V <sub>DS</sub> = 0                  |        |        |         |          |

|      |                                                                                 | Gate No. 2  | V <sub>(BR)G2SSF</sub> | 100 μ A                                                                      |                                                                                         | s = V <sub>DS</sub> = 0                  | 6.5    | -      | 13      | V        |

|      | ate-to-Source Reverse<br>reakdown Voltage                                       | Gate No. 1  | V <sub>(BR)G1SSR</sub> | I <sub>G1SSR</sub> = V <sub>G2S</sub>                                        |                                                                                         | $V_{G30} = V_{D0} = 0$                   |        | -      | 10      |          |

|      |                                                                                 | Gate No. 2  | V <sub>(BR)G2SSR</sub> |                                                                              |                                                                                         | s = V <sub>DS</sub> = 0                  | -6.5   | -      | - 13    | ٧        |

$<sup>^{\</sup>uparrow}$  Capacitance between Gate No. 1 and all other terminals.  $\bullet$  Three-terminal measurement with Gate No. 2 and

#### OPERATING CONSIDERATIONS

The flexible leads of the 3N200 are usually soldered to the circuit elements. As in the case of any high-frequency semiconductor device, the tips of soldering irons MUST be grounded.

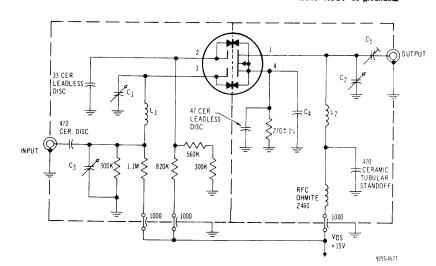

All resistances in ohms All capacitances in pF

C<sub>1</sub>, C<sub>2</sub>: 1.3-5.4 pF variable air capacitor: Hammerland Mac 5 type or equivalent

C<sub>3</sub>: 1.9-13.8 pF variable air capacitor: Hammerland Mac 15 type or equivalent

C<sub>4</sub>: Approx. 300 pF-capacitance formed between socket cover & chassis

C<sub>5</sub>: 0.8-4.5 pF piston type variable air capacitor: Erie 560-013 or equivalent

$L_1,L_2$ : Inductance to tune circuit

Fig. 1 - 400 MHz power gain and noise figure test circuit

Source returned to guard terminal.

<sup>\*</sup>In accordance with JEDEC registration data format (JS-9 RDF-19A)

# Typical Characteristics

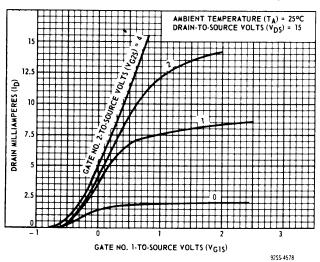

Fig. 2-ID vs. VG1S

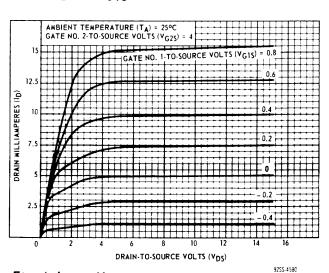

Fig. 4-1<sub>D</sub> vs. V<sub>DS</sub>

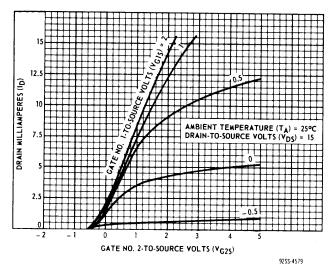

Fig. 3-ID vs. VG2S

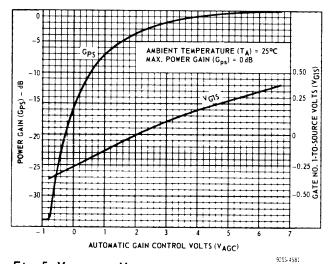

Fig. 5- VAGC vs. VGIS

y and s Parameters vs. Frequency

TEST CONDITIONS: Drain-to-Source Volts ( $V_{DS}$ ) = 15, Drain Milliamperes ( $I_{D}$ ) = 10, Gate No. 2-to-Source Volts ( $V_{G2S}$ ) = 4

| CHARACTERISTICS                                                | SYMBOL            | FREQUENCY (MHz) |        |       |       |        | UNITS   |

|----------------------------------------------------------------|-------------------|-----------------|--------|-------|-------|--------|---------|

|                                                                |                   | 100             | 200    | 300   | 400   | 500    |         |

| Maximum Available Power Gain                                   | MAG               | 32              | 24     | 17.5  | 13    | 10     | dB      |

| Maximum Usable Power Gain (Unneutralized)* <u>Y Parameters</u> | MUG               | 32              | 24     | 17.5  | 13    | 10     | dB      |

| Input Conductance                                              | gis               | 0.25            | 0.8    | 2.0   | 3.6   | 6.2    | mmho    |

| Input Susceptance                                              | bis               | 3.4             | 5.8    | 8.5   | 11.2  | 15.5   | mmho    |

| Magnitude of Forward Transadmittance                           | yfs               | 15.3            | 15.3   | 15.4  | 15.5  | 16.3   | mmho    |

| Angle of Forward Transadmittance                               | ∠yfs              | - 15            | - 25   | - 35  | - 47  | - 60   | degrees |

| Output Conductance                                             | g <sub>os</sub> · | 0.15            | 0.3    | 0.5   | 0.8   | 1.1    | mmho    |

| Output Susceptance                                             | b <sub>os</sub>   | 1.5             | 2.7    | 3.6   | 4.25  | 5.0    | mmho    |

| Magnitude of Reverse Transadmittance                           | y <sub>rs</sub>   | 0.012           | 0.025  | 0.06  | 0.14  | 0.26   | mmho    |

| Angle of Reverse Transadmittance S Parameters                  | ∠yrs              | - 60            | - 25   | 0     | 14    | 20     | degrees |

| Magnitude of Input Reflection Coeff.                           | sis               | 0.97            | 0.90   | 0.84  | 0.78  | 0.70   |         |

| Angle of Input Reflection Coeff.                               | ∠s <sub>is</sub>  | - 20            | - 32   | - 55  | - 68  | -82    | degrees |

| Magnitude of Forward Transmission Coeff.                       | Sfs               | 1.50            | 1.40   | 1.25  | 1.1   | 0.9    | dogices |

| Angle of Forward Transmission Coeff.                           | ∠s <sub>fs</sub>  | 153             | 133    | 112   | 90    | 70     | degrees |

| Mangitude of Output Reflection Coeff.                          | Sos               | 0.985           | 0.95   | 0.93  | 0.92  | 0.91   |         |

| Angle of Output Reflection Coeff.                              | ∠s <sub>os</sub>  | -7.5            | - 16   | - 22  | - 28  | - 34   | degrees |

| Magnitude of Reverse Transmission Coeff.                       | [srs]             | 0.001           | 0.0025 | 0.005 | 0.010 | 0.0165 | 6,000   |

| Angle of Reverse Transmission Coeff.                           | ∠s <sub>rs</sub>  | 100             | 125    | 141   | 150   | 142    | degrees |

<sup>\*</sup>Limited only by practical design considerations

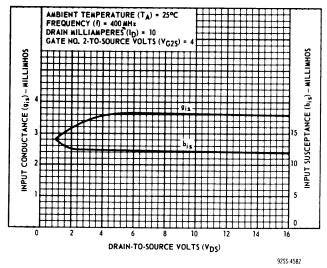

# Typical y Parameters vs. VDS

Fig. 6-yis vs. VDS

DRAIN-TO-SOURCE VOLTS (VDS)

Fig. 8-yfs vs. VDS

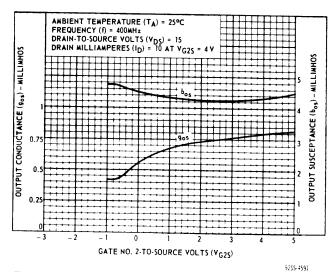

Fig. 7-yos vs. VDS

Fig. 9-yrs vs. VDS

# Typical y Parameters vs ID

9255-4584

Fig. 10-yis vs. ID

Fig. 11-y<sub>os</sub> vs. ID

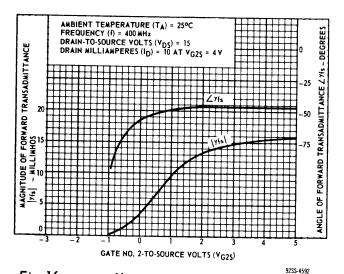

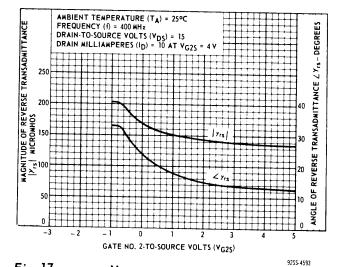

# Typical y Parameters vs. ID (cont'd)

Fig. 12-yfs vs. ID

Fig. 13 - y<sub>rs</sub> vs. ID

Typical y Parameters vs. V<sub>G2S</sub>

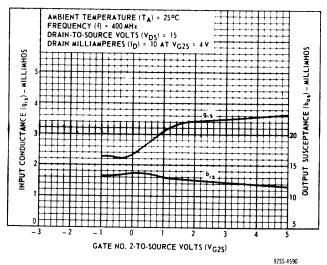

Fig. 14 - yis vs. VG2S

Fig. 15 - yos vs. VG2S

Fig. 16 - yfs vs. VG2S

Fig. 17 - y<sub>rs</sub> vs. V<sub>G2S</sub>

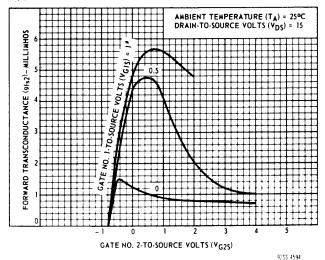

## Typical Characteristics

Fig. 18 - gfs2 vs. VG2S

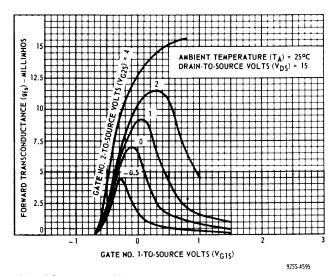

Fig. 19 - gfs vs. VG1S

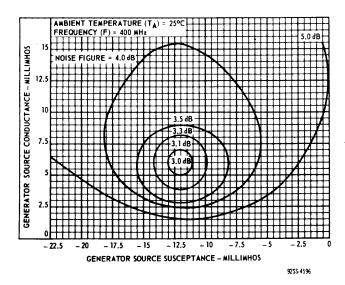

Fig. 20 - Noise figure vs. generator source admittance

# DIMENSIONAL OUTLINE JEDEC TO-72

Dimensions in Inches and Millimeters

Note 1: Dimensions in parentheses are in millimeters and are derived from the basic inch dimensions as indicated.

Note 2: The specified lead diameter applies in the zone between 0.050" (1.27 mm) and 0.250" (6.35 mm) from the seating plane. From 0.250" (6.35 mm) to the end of the lead a maximum diameter of 0.021" (0.533 mm) is held. Outside of these zones, the lead diameter is not controlled.

Note 3: Leads having a maximum diameter of 0.019" (0.482 mm) at a guaging plane of 0.054" (1.372 mm) + 0.001" (0.025 mm) -0.000" (0.000 mm) below seating plane shall be within 0.007" (0.177 mm) at their true position (location) relative to a maximum width of tab.

Note 4: Measured from actual maximum diameter.

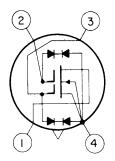

## TERMINAL DIAGRAM

LEAD 1-DRAIN LEAD 2-GATE No. 2 LEAD 3-GATE No. 1 LEAD 4-SOURCE, SUBSTRATE AND CASE

Information furnished by RCA is believed to be accurate and reliable. However, no responsibility is assumed by RCA for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of RCA.