## MOTOROLA SEMICONDUCTOR TECHNICAL DATA

## **MRF140**

## The RF TMOS Line

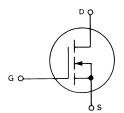

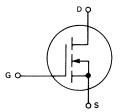

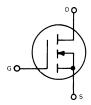

#### N-CHANNEL ENHANCEMENT-MODE TMOS RF POWER FIELD-EFFECT TRANSISTOR

- . . designed primarily for linear large-signal output stages in the 2-150 MHz frequency range.

- Specified 28 Volts, 30 MHz Characteristics

Output Power = 150 Watts Power Gain = 15 dB (Typ) Efficiency = 40% (Typ)

- Superior High Order IMD

- IMD(d3) (150 W PEP) = -30 dB Typ

- IMD(d11) (150 W PEP) = -60 dB Typ

- 100% Tested For Load Mismatch At All Phase Angles With 30:1 VSWR

#### **MAXIMUM RATINGS**

| Symbol           | Value                    | Unit                                                      |

|------------------|--------------------------|-----------------------------------------------------------|

| V <sub>DSS</sub> | 65                       | Vdc                                                       |

| V <sub>DGO</sub> | 65                       | Vdc                                                       |

| V <sub>GS</sub>  | ± 40                     | Vdc                                                       |

| ID               | 16                       | Adc                                                       |

| PD               | 300<br>1.7               | Watts<br>W/°C                                             |

| T <sub>stg</sub> | -65 to +150              | °C                                                        |

| ΤJ               | 200                      | °C                                                        |

|                  | VDSS VDGO VGS ID PD Tstg | VDSS 65 VDGO 65 VGS ±40 ID 16 PD 300 1.7 Tstg -65 to +150 |

#### THERMAL CHARACTERISTICS

| Characteristic                       | Symbol          | Max | Unit |

|--------------------------------------|-----------------|-----|------|

| Thermal Resistance, Junction to Case | $R_{\theta JC}$ | 0.6 | °C/W |

Handling and Packaging — MOS devices are susceptible to damage from electrostatic charge. Reasonable precautions in handling and packaging MOS devices should be observed.

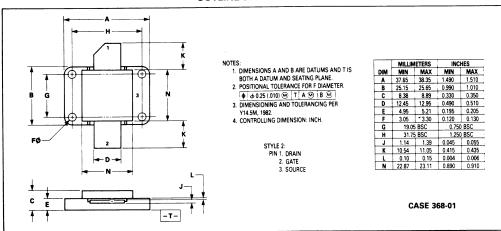

#### 150 W 2.0-150 MHz

**N-CHANNEL TMOS** LINEAR RF POWER **FET**

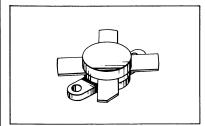

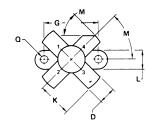

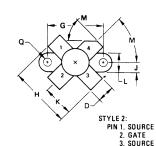

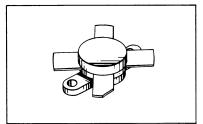

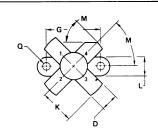

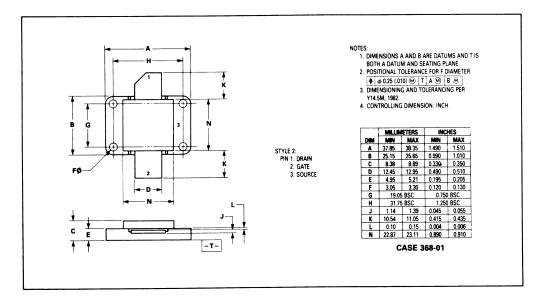

STYLE 2: PIN 1. SOURCE 2. GATE 3. SOURCE 4. DRAIN

|     | MILLIMETERS |       | INC     | HES   |

|-----|-------------|-------|---------|-------|

| DIM | MIN         | MAX   | MIN     | MAX   |

| Α   | 24.38       | 25.15 | 0.960   | 0.990 |

| В   | 11.81       | 12.95 | 0.465   | 0.510 |

| C   | 5.82        | 6.98  | 0.229   | 0.275 |

| D   | 5.46        | 5.97  | 0.216   | 0.235 |

| E   | 2.13        | 2.79  | 0.084   | 0.110 |

| F   | 0.08        | 0.18  | 0.003   | 0.007 |

| G   | 18.29       | 18.54 | 0.720   | 0.730 |

| К   | 11.05       | -     | 0.435   |       |

| L   | 6.22        | 6.48  | 0.246   | 0.255 |

| M   | 450         | NOM   | 450 NOM |       |

| N   | 3.66        | 4.52  | 0.144   | 0.178 |

| a   | 2.92        | 3.30  | 0.115   | 0.130 |

**CASE 211-11**

### ELECTRICAL CHARACTERISTICS (T<sub>C</sub> = 25°C unless otherwise noted)

| Characteristic                                                                                                                                            | Symbol                                      | Min                            | Тур        | Max | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------|------------|-----|------|

| OFF CHARACTERISTICS                                                                                                                                       |                                             |                                |            |     |      |

| Drain-Source Breakdown Voltage<br>(VGS = 0, I <sub>D</sub> = 100•mA)                                                                                      | V <sub>(BR)DSS</sub>                        | 65                             | _          | _   | Vdc  |

| Zero Gate Voltage Drain Current<br>(V <sub>DS</sub> = 28 Vdc, V <sub>GS</sub> = 0)                                                                        | IDSS                                        | _                              | _          | 5.0 | mAdc |

| Gate-Body Leakage Current<br>(V <sub>G</sub> S = 20 Vdc, V <sub>D</sub> S = 0)                                                                            | l <sub>GSS</sub>                            | _                              |            | 1.0 | μAdc |

| ON CHARACTERISTICS                                                                                                                                        |                                             |                                |            |     |      |

| Gate Threshold Voltage<br>(V <sub>DS</sub> = 10 V, I <sub>D</sub> = 100 mA)                                                                               | VGS(th)                                     | 1.0                            | 3.0        | 5.0 | Vdc  |

| Drain-Source On-Voltage<br>(VGS = 10 V, I <sub>D</sub> = 10 Adc)                                                                                          | V <sub>DS(on)</sub>                         |                                | _          | 1.5 | Vdc  |

| Forward Transconductance<br>(V <sub>DS</sub> = 10 V, I <sub>D</sub> = 5.0 A)                                                                              | 9fs                                         | 4.0                            | _          | -   | mhos |

| DYNAMIC CHARACTERISTICS                                                                                                                                   |                                             |                                |            |     |      |

| Input Capacitance<br>(V <sub>DS</sub> = 28 V, V <sub>GS</sub> = 0, f = 1.0 MHz)                                                                           | C <sub>iss</sub>                            | _                              | 450        | _   | pF   |

| Output Capacitance<br>(V <sub>DS</sub> = 28 V, V <sub>GS</sub> = 0, f = 1.0 MHz)                                                                          | C <sub>oss</sub>                            | _                              | 450        | _   | pF   |

| Reverse Transfer Capacitance<br>(V <sub>DS</sub> = 28 V, V <sub>GS</sub> = 0, f = 1.0 MHz)                                                                | C <sub>rss</sub>                            | _                              | 100        | _   | pF   |

| FUNCTIONAL TESTS (SSB)                                                                                                                                    |                                             |                                |            |     |      |

| Common Source Amplifier Power Gain (30 MHz) (VDD = 28 V, Pout = 150 W (PEP), IDQ = 250 mA) (150 MHz)                                                      | G <sub>ps</sub>                             | _                              | 15<br>6.0  | _   | dB   |

| Drain Efficiency<br>(V <sub>DD</sub> = 28 V. P <sub>out</sub> = 150 W (PEP), f = 30; 30.001 MHz,<br>I <sub>D</sub> (Max) = 6.5 A)                         | η                                           | _                              | 40         | _   | %    |

| Intermodulation Distortion (1)<br>(V <sub>DD</sub> = 28 V, P <sub>Out</sub> = 150 W (PEP), f1 = 30 MHz,<br>f2 = 30.001 MHz, I <sub>DQ</sub> = 250 mA)     | IMD <sub>(d3)</sub><br>IMD <sub>(d11)</sub> | _                              | -30<br>-60 | _   | dB   |

| Load Mismatch<br>(V <sub>DD</sub> = 28 V, P <sub>out</sub> = 150 W (PEP), f = 30; 30.001 MHz,<br>I <sub>DQ</sub> = 250 mA, VSWR 30:1 at all Phase Angles) | ψ                                           | No Degradation in Output Power |            |     |      |

<sup>(1)</sup> To MIL-STD-1311 Version A, Test Method 2204B, Two Tone, Reference Each Tone.

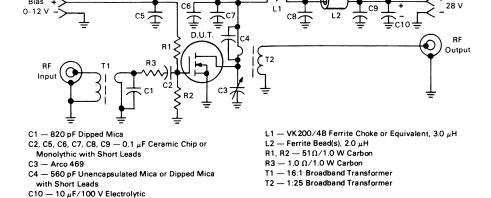

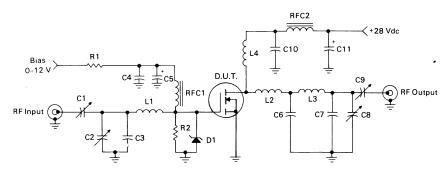

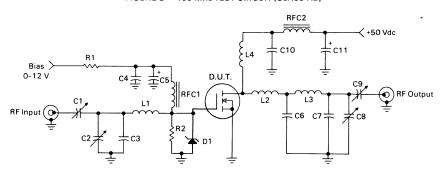

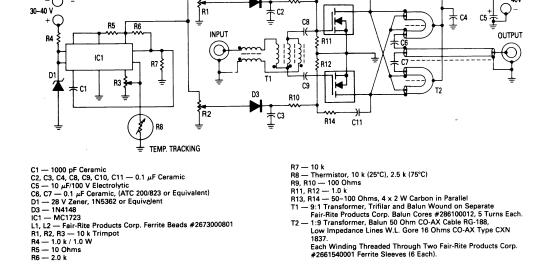

## FIGURE 1 - 30 MHz TEST CIRCUIT (CLASS AB)

FIGURE 7 - SERIES EQUIVALENT IMPEDANCE

FIGURE 8 - 150 MHz TEST CIRCUIT (CLASS AB)

C1, C2, C8 — Arco 463 or equivalent

${

m C3-25~pF~Unelco}$

${

m C4-0.1~\mu F~Ceramic}$

C5 — 1.0  $\mu$ F, 15 WV Tantalum

C6 — 150 pF Unelco J101

C7 — 25 μF Unelco J101

${

m C9-Arco\,262}$  or equivalent

${\rm C10-0.05~\mu F~Ceramic}$

C11 — 15  $\mu$ F, 35 WV Electrolytic

$\rm L1 - 3/4$ " #18 AWG into Hairpin

L2 — Printed Line, 0.200" × 0.500"

L3 — 7/8" #16 AWG into Hairpin L4 — 2 Turns #16 AWG, 5/16 ID

RFC1 — 5.6  $\mu$ H Molded Choke

RFC2 — VK200-4B

R1, R2 - 150  $\Omega$ , 1.0 W Carbon

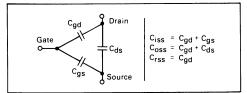

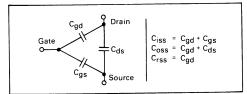

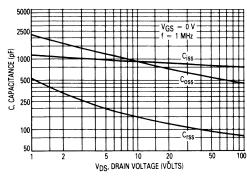

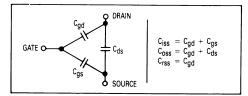

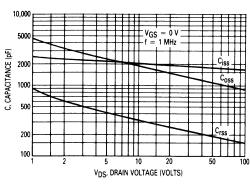

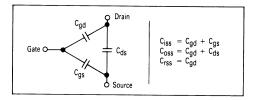

#### MOSFET CAPACITANCES

The physical structure of a MOSFET results in capacitors between the terminals. The metal oxide gate structure determines the capacitors from gate-to-drain (Cgd), and gate-to-source (Cgs). The PN junction formed during the fabrication of the TMOS FET results in a junction capacitance from drain-to-source (Cds).

These capacitances are characterized as input  $(C_{iss})$ , output  $(C_{oss})$  and reverse transfer  $(C_{rss})$  capacitances on data sheets. The relationships between the interminal capacitances and those given on data sheets are shown below. The  $C_{iss}$  can be specified in two ways:

- Drain shorted to source and positive voltage at the gate.

- Positive voltage of the drain in respect to source and zero volts at the gate. In the latter case the numbers are lower. However, neither method represents the actual operating conditions in RF applications.

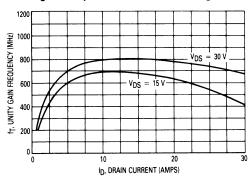

#### LINEARITY AND GAIN CHARACTERISTICS

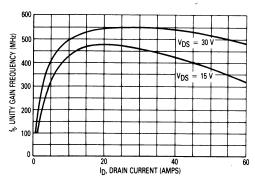

In addition to the typical IMD and power gain data presented, Figure 5 may give the designer additional information on the capabilities of this device. The graph represents the small signal unity current gain frequency at a given drain current level. This is equivalent to f $_{\rm T}$  for bipolar transistors. Since this test is performed at a fast sweep speed, heating of the device does not occur. Thus, in normal use, the higher temperatures may degrade these characteristics to some extent.

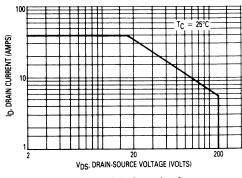

#### **DRAIN CHARACTERISTICS**

One figure of merit for a FET is its static resistance in the full-on condition. This on-resistance,  $V_{DS(on)}$ , occurs in the linear region of the output characteristic and is specified under specific test conditions for gate-source voltage and drain current. For MOSFETs,  $V_{DS(on)}$  has a positive temperature coefficient and constitutes an important design consideration at high temperatures, because it contributes to the power dissipation within the device.

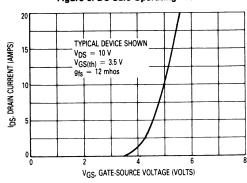

#### **GATE CHARACTERISTICS**

The gate of the TMOS FET is a polysilicon material, and is electrically isolated from the source by a layer of oxide. The input resistance is very high — on the order of  $10^9$  ohms — resulting in a leakage current of a few nanoamperes.

Gate control is achieved by applying a positive voltage slightly in excess of the gate-to-source threshold voltage,  $V_{GS(th)}$ .

**Gate Voltage Rating** — Never exceed the gate voltage rating. Exceeding the rated VGS can result in permanent damage to the oxide layer in the gate region.

Gate Termination — The gates of these devices are essentially capacitors. Circuits that leave the gate open-circuited or floating should be avoided. These conditions can result in turn-on of the devices due to voltage build-up on the input capacitor due to leakage currents or pickup.

Gate Protection — These devices do not have an internal monolithic zener diode from gate-to-source. If gate protection is required, an external zener diode is recommended.

#### **EQUIVALENT TRANSISTOR PARAMETER TERMINOLOGY**

| Collector           | <br>Drain             |

|---------------------|-----------------------|

| Emitter             | <br>Source            |

| Base                | <br>Gate              |

| V(BR)CES            | <br>V(BR)DSS          |

| Vсво                | <br>V <sub>DGO</sub>  |

| IС                  | <br>ID                |

| ICES                | <br>IDSS              |

|                     |                       |

|                     |                       |

|                     |                       |

|                     |                       |

|                     |                       |

|                     |                       |

| RCE(sat) = VCE(sat) | <br>rns(on) = VDS(on) |

| "CE(sat/ - IC       | <br>. Da(oii) ID      |

|                     |                       |

# MOTOROLA SEMICONDUCTOR TECHNICAL DATA

## **MRF148**

## The RF TMOS Line

## N-CHANNEL ENHANCEMENT-MODE TMOS RF POWER FIELD-EFFECT TRANSISTOR

... designed for power amplifier applications in industrial, commercial and amateur radio equipment to 175 MHz.

- Superior High Order IMD

- Specified 50 Volts, 30 MHz Characteristics

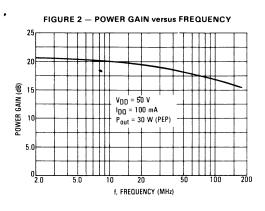

Output Power = 30 Watts Power Gain = 18 dB (Typ) Efficiency = 40% (Typ)

- IMD(d3) (30 W PEP) = -35 dB (Typ)

- IMD(d11) (30 W PEP) = -60 dB (Typ)

- 100% Tested For Load Mismatch At All Phase Angles With 30:1 VSWR

#### **MAXIMUM RATINGS**

| Rating                                                                | Symbol           | Value       | Unit          |

|-----------------------------------------------------------------------|------------------|-------------|---------------|

| Drain — Source Voltage                                                | VDSS             | 120         | Vdc           |

| Drain — Gate Voltage                                                  | V <sub>DGO</sub> | 120         | Vdc           |

| Gate — Source Voltage                                                 | VGS              | ± 40        | Vdc           |

| Drain Current — Continuous                                            | ID               | 6.0         | Adc           |

| Total Device Dissipation @ T <sub>C</sub> = 25°C<br>Derate above 25°C | PD               | 115<br>0.66 | Watts<br>W/°C |

| Storage Temperature Range                                             | T <sub>stg</sub> | -65 to +150 | °C            |

| Operating Junction Temperature                                        | TJ               | 200         | °C            |

#### THERMAL CHARACTERISTICS

| Characteristic                       | Symbol          | Max  | Unit |

|--------------------------------------|-----------------|------|------|

| Thermal Resistance, Junction to Case | $R_{\theta JC}$ | 1.52 | °C/W |

Handling and Packaging — MOS devices are susceptible to damage from electrostatic charge. Reasonable precautions in handling and packaging MOS devices should be observed.

#### 30 W 2.0-175 MHz

## N-CHANNEL TMOS LINEAR RF POWER FET

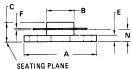

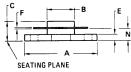

| [C   → B      |                  |

|---------------|------------------|

| ₩ F           | ſ <sup>E</sup> • |

|               | N                |

| \             | 4 4              |

| SEATING PLANE |                  |

4. DRAIN

|     | MILLIMETERS |       | INC   | HES   |

|-----|-------------|-------|-------|-------|

| DIM | MIN         | MAX   | MIN   | MAX   |

| Α   | 24.38       | 25.15 | 0.960 | 0.990 |

| В   | 9.40        | 9.91  | 0.370 | 0.390 |

| C   | 5.82        | 7.14  | 0.229 | 0.281 |

| D   | 5.46        | 5.97  | 0.215 | 0.235 |

| E   | 2.16        | 2.67  | 0.085 | 0.105 |

| F   | 0.10        | 0.15  | 0.004 | 0.006 |

| G   | 18.29       | 18.54 | 0.720 | 0.730 |

| H   | 20.07       | 20.57 | 0.790 | 0.810 |

| K   | 10.03       | 10.29 | 0.395 | 0.405 |

| L   | 6.22        | 6.48  | 0.245 | 0.255 |

| M   | 40°         | 50°   | 40°   | 50°   |

| N   | 3.81        | 4.57  | 0.150 | 0.180 |

| Q   | 2.87        | 3.30  | 0.113 | 0.130 |

CASE 211-07

### ELECTRICAL CHARACTERISTICS (T<sub>C</sub> = 25°C unless otherwise noted)

| Characteristic                                                                                                                                               | Symbol                                               | Min                            | Тур              | Max | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------|------------------|-----|------|

| OFF CHARACTERISTICS                                                                                                                                          |                                                      |                                |                  |     |      |

| Drain-Source Breakdown Voltage<br>(V <sub>GS</sub> = 0, I <sub>D</sub> = 10 mA)                                                                              | V(BR)DSS                                             | 125                            | _                |     | Vdc  |

| Zero Gate Voltage*Drain Current<br>(V <sub>DS</sub> = 50 V, V <sub>GS</sub> = 0.)                                                                            | IDSS                                                 | _                              | _                | 1.0 | mAdc |

| Gate-Body Leakage Current<br>(V <sub>GS</sub> = 20 V, V <sub>DS</sub> = 0)                                                                                   | IGSS                                                 | -                              |                  | 100 | nAdc |

| ON CHARACTERISTICS                                                                                                                                           |                                                      |                                |                  |     |      |

| Gate Threshold Voltage (V <sub>DS</sub> = 10 V, I <sub>D</sub> = 10 mA)                                                                                      | V <sub>GS(th)</sub>                                  | 1.0                            | 3.0              | 5.0 | Vdc  |

| Drain-Source On-Voltage<br>(V <sub>GS</sub> = 10 V, I <sub>D</sub> = 2.5 A)                                                                                  | V <sub>DS(on)</sub>                                  | _                              | _                | 5.0 | Vdc  |

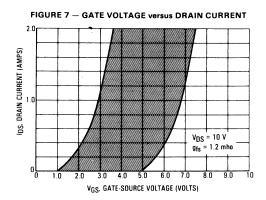

| Forward Transconductance<br>(V <sub>DS</sub> = 10 V, I <sub>D</sub> = 2.5 A)                                                                                 | 9fs                                                  | 0.8                            | 1.2              | _   | mhos |

| DYNAMIC CHARACTERISTICS                                                                                                                                      |                                                      |                                |                  |     |      |

| Input Capacitance<br>(V <sub>DS</sub> = 50 V, V <sub>GS</sub> = 0 V, f = 1.0 MHz)                                                                            | C <sub>iss</sub>                                     | _                              | 50               | _   | pF   |

| Output Capacitance<br>(V <sub>DS</sub> = 50 V, V <sub>GS</sub> = 0, f = 1.0 MHz)                                                                             | C <sub>oss</sub>                                     |                                | 35               | _   | pF   |

| Reverse Transfer Capacitance<br>(V <sub>DS</sub> = 50 V, V <sub>GS</sub> = 0, f = 1.0 MHz)                                                                   | C <sub>rss</sub>                                     | _                              | 8.0              | _   | pF   |

| FUNCTIONAL TESTS (SSB)                                                                                                                                       |                                                      |                                |                  |     |      |

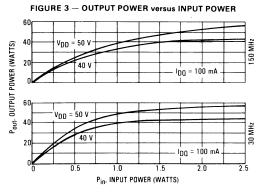

| Common Source Amplifier Power Gain (30 MHz)<br>(V <sub>DD</sub> = 50 V, P <sub>out</sub> = 30 W (PEP), I <sub>DQ</sub> = 100 mA) (175 MHz)                   | G <sub>ps</sub>                                      | _                              | 18<br>15         | _   | dB   |

|                                                                                                                                                              | η                                                    | _                              | 40<br>50         | _   | %    |

| Intermodulation Distortion<br>(V <sub>DD</sub> = 50 V, P <sub>out</sub> = 30 W (PEP),<br>f = 30; 30.001 MHz, I <sub>DQ</sub> = 100 mA)                       | IMD <sub>(d3)</sub><br>IMD <sub>(d11)</sub>          | _                              | -35<br>-60       | _   | dB   |

| Load Mismatch<br>(V <sub>DD</sub> = 50 V, P <sub>Out</sub> = 30 W (PEP), f = 30; 30.001 MHz,<br>I <sub>DQ</sub> = 100 mA, VSWR 30:1 at all Phase Angles)     | ψ                                                    | No Degradation in Output Power |                  |     |      |

| CLASS A PERFORMANCE                                                                                                                                          |                                                      |                                |                  |     |      |

| Intermodulation Distortion (1) and Power Gain (V <sub>DD</sub> = 50 V, P <sub>out</sub> = 10 W (PEP), f1 = 30 MHz, f2 = 30.001 MHz, I <sub>DO</sub> = 1.0 A) | GPS<br>IMD <sub>(d3)</sub><br>IMD <sub>(d9-13)</sub> | _<br>_<br>_                    | 20<br>-50<br>-70 |     | dB   |

<sup>(1)</sup> To MIL-STD-1311 Version A, Test Method 2204B, Two Tone, Reference Each Tone.

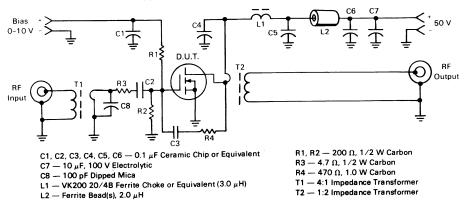

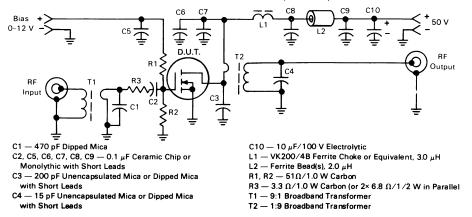

#### FIGURE 1 - 2-50 MHz BROADBAND TEST CIRCUIT

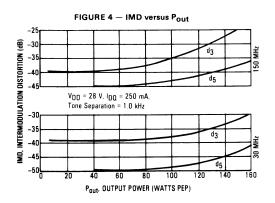

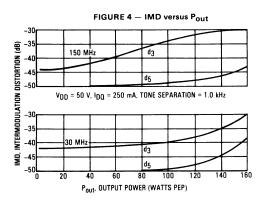

FIGURE 4 — IMD versus Pout

(99)

VDD = 50 V. IDQ = 100 mA, TONE SEPARATION 1.0 kHz

VDD = 50 V. IDQ = 100 mA, TONE SEPARATION 1.0 kHz

Pout: OUTPUT POWER (WATTS PEP)

L1 — 2 Turns # 18 AWG, 5/16" ID

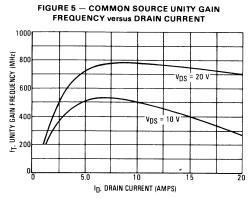

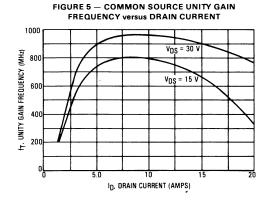

FIGURE 5 — COMMON SOURCE UNITY GAIN

FREQUENCY versus DRAIN CURRENT

VDS = 30 V

VDS = 15 V

ID, DRAIN CURRENT (AMPS)

FIGURE 6 - 150 MHz TEST CIRCUIT Bias R2 O +50 Vdc RFC1 0-6 V RF Output D.U.T. C7 RF Input L1 C6 C1 — 91 pF Unelco Type MCM 01/010 L2 — 4 Turns # 18 AWG, 5/16" ID C2, C4 - 0.1  $\mu F$  Erie Red Cap R1 = 1.0 Ohm, 1/4 W Carbon C3 — Allen Bradley 680 pF Feed Thru R2 — 2000 Ohm, 1/4 W Carbon  $C5-1.0~\mu F$ , 50 Vdc Electrolytic RFC1 - VK200 21/4B 4:1 Impedance Ratio C6 — 15 pF Unelco Type J101 T1 — 4:1 Transformer, 1.75" Transformer, Line Impedance = 25  $\Omega$ C7 — 24 pF Unelco Type MCM 01/010 Subminiature Coaxial Cable

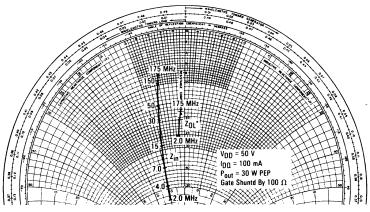

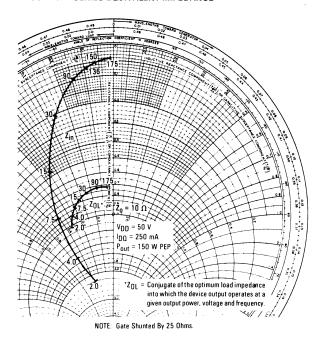

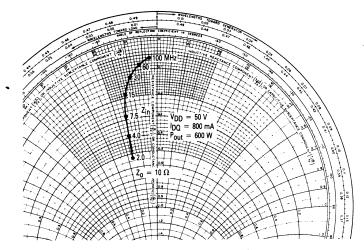

FIGURE 9 — IMPEDANCE COORDINATES — 50-OHM CHARACTERISTIC IMPEDANCE

\*Z<sub>OL</sub> = Conjugate of the optimun load impedance into which the device output operates at a given output power, voltage and frequency.

#### **MOSFET CAPACITANCES**

The physical structure of a MOSFET results in capacitors between the terminals. The metal oxide gate structure determines the capacitors from gate-to-drain (Cgd), and gate-to-source (Cgs). The PN junction formed during the fabrication of the TMOS FET results in a junction capacitance from drain-to-source (Cds).

These capacitances are characterized as input ( $C_{iss}$ ), output ( $C_{oss}$ ) and reverse transfer ( $C_{rss}$ ) capacitances on data sheets. The relationships between the inter-terminal capacitances and those given on data sheets are shown below. The  $C_{iss}$  can be specified in two ways:

- Drain shorted to source and positive voltage at the gate.

- Positive voltage of the drain in respect to source and zero volts at the gate. In the latter case the numbers are lower. However, neither method represents the actual operating conditions in RF applications.

$$\begin{array}{c|c} C_{gd} & Drain \\ \hline \\ C_{ds} & C_{ds} \\ \hline \\ C_{gs} & Source \end{array} \quad \begin{array}{c|c} C_{iss} = C_{gd} + C_{gs} \\ C_{oss} = C_{gd} + C_{ds} \\ C_{rss} = C_{gd} \end{array}$$

### **LINEARITY AND GAIN CHARACTERISTICS**

In addition to the typical IMD and power gain data presented, Figure 5 may give the designer additional information on the capabilities of this device. The graph represents the small signal unity current gain frequency at a given drain current level. This is equivalent to fT for bipolar transistors. Since this test is performed at a fast sweep speed, heating of the device does not occur. Thus, in normal use, the higher temperatures may degrade these characteristics to some extent.

#### **DRAIN CHARACTERISTICS**

One figure of merit for a FET is its static resistance in the full-on condition. This on-resistance, VDS(on), occurs in the linear region of the output characteristic and is specified under specific test conditions for gate-source voltage and drain current. For MOSFETs, VDS(on) has a positive temperature coefficient and constitutes an important design consideration at high temperatures, because it contributes to the power dissipation within the device

#### **GATE CHARACTERISTICS**

The gate of the TMOS FET is a polysilicon material, and is electrically isolated from the source by a layer of oxide. The input resistance is very high — on the order of  $10^9$  ohms — resulting in a leakage current of a few nanoamperes.

Gate control is achieved by applying a positive voltage slightly in excess of the gate-to-source threshold voltage, VGS(th).

Gate Voltage Rating — Never exceed the gate voltage rating. Exceeding the rated VGS can result in permanent damage to the oxide layer in the gate region.

Gate Termination — The gates of these devices are essentially capacitors. Circuits that leave the gate open-circuited or floating should be avoided. These conditions can result in turn-on of the devices due to voltage build-up on the input capacitor due to leakage currents or pickup.

Gate Protection — These devices do not have an internal monolithic zener diode from gate-to-source. If gate protection is required, an external zener diod is recommended.

#### **EQUIVALENT TRANSISTOR PARAMETER TERMINOLOGY**

| Collector                               | <br>Drain                                   |

|-----------------------------------------|---------------------------------------------|

| Emitter                                 | <br>Source                                  |

| Base                                    | <br>Gate                                    |

| V(BR)CES                                | <br>V(BR)DSS                                |

| V <sub>СВО</sub>                        | <br>V <sub>DGO</sub>                        |

| ΙC                                      | <br>۱D                                      |

| <sup>I</sup> CES                        | <br>IDSS                                    |

| <sup>I</sup> EBO                        | <br>IGSS                                    |

| V <sub>BE(on)</sub>                     | <br>VGS(th)                                 |

| V <sub>CE(sat)</sub>                    | <br>V <sub>DS(on)</sub>                     |

| C <sub>ib</sub>                         | <br>C <sub>iss</sub>                        |

| C <sub>ob</sub>                         | <br>Coss                                    |

| h <sub>fe</sub>                         | <br>9fs                                     |

| $R_{CE(sat)} = \frac{V_{CE(sat)}}{I_C}$ | <br>$r_{DS(on)} = \frac{V_{DS(on)}}{I_{D}}$ |

# MOTOROLA SEMICONDUCTOR I TECHNICAL DATA

## **MRF150**

## The RF TMOS Line

# N-CHANNEL ENHANCEMENT-MODE TMOS RF POWER FIELD-EFFECT TRANSISTOR

... designed primarily for linear large-signal output stages in the 2–175 MHz frequency range.

Specified 50 Volts, 30 MHz Characteristics

Output Power = 150 Watts Power Gain = 17 dB (Typ) Efficiency = 45% (Typ)

- Superior High Order IMD

- IMD(d3) (150 W PEP) = -32 dB (Typ)

- IMD<sub>(d11)</sub> (150 W PEP) = −60 dB (Typ)

- 100% Tested For Load Mismatch At All Phase Angles With 30:1 VSWR

#### MAXIMUM RATINGS

| Rating                                                             | Symbol            | Value       | Unit          |

|--------------------------------------------------------------------|-------------------|-------------|---------------|

| Drain — Source Voltage                                             | V <sub>DSS</sub>  | 125         | Vdc           |

| Drain — Gate Voltage                                               | V <sub>D</sub> GO | 125         | Vdc           |

| Gate — Source Voltage                                              | V <sub>GS</sub>   | ± 40        | Vdc           |

| Drain Current — Continuous                                         | 1 <sub>D</sub>    | 16          | Adc           |

| Total Device Dissipation @ T <sub>C</sub> = 25°C Derate above 25°C | PD                | 300<br>1.71 | Watts<br>W/°C |

| Storage Temperature Range                                          | T <sub>stg</sub>  | -65 to +150 | °C            |

| Operating Junction Temperature                                     | TJ                | 200         | °C            |

#### THERMAL CHARACTERISTICS

| Characteristic                       | Symbol          | Max | Unit |

|--------------------------------------|-----------------|-----|------|

| Thermal Resistance, Junction to Case | $R_{\theta}$ JC | 0.6 | °C/W |

Handling and Packaging — MOS devices are susceptible to damage from electrostatic charge. Reasonable precautions in handling and packaging MOS devices should be observed.

#### 150 W 2.0-175 MHz

## N-CHANNEL TMOS LINEAR RF POWER FET

STYLE 2: PIN 1. SOURCE

2. GATE 3. SOURCE 4. DRAIN

|     | MILLIMETERS     |       | INC   | HES   |

|-----|-----------------|-------|-------|-------|

| DIM | MIN             | MAX   | MIN   | MAX   |

| Α   | 24.38           | 25.15 | 0.960 | 0.990 |

| В   | 11.81           | 12.95 | 0.465 | 0.510 |

| C   | 5.82            | 6.98  | 0.229 | 0.275 |

| D   | 5.46            | 5,97  | 0.216 | 0.235 |

| E   | 2.13            | 2.79  | 0.084 | 0.110 |

| F   | 0.08            | 0.18  | 0.003 | 0.007 |

| G   | 18.29           | 18.54 | 0.720 | 0.730 |

| K   | 11.05           | -     | 0.435 | -     |

| L   | 6.22            | 6.48  | 0.246 | 0.255 |

| M   | 45 <sup>0</sup> | NOM   | 450   | NOM   |

| N   | 3.66            | 4.52  | 0.144 | 0.178 |

| Q   | 2.92            | 3.30  | 0.115 | 0.130 |

CASE 211-11

### ELECTRICAL CHARACTERISTICS (T<sub>C</sub> = 25°C unless otherwise noted)

| Characteristic                                                                                                                                               | Symbol                                               | Min                            | Тур              | Max         | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------|------------------|-------------|------|

| OFF CHARACTERISTICS                                                                                                                                          |                                                      |                                |                  |             |      |

| Drain-Source Breakdown Voltage<br>(VGS = 0, ID = 100 mA)                                                                                                     | V(BR)DSS                                             | 125                            | _                | -           | Vdc  |

| Zero Gate Voltage Drain Current (VDS = 50 V, VGS = 0)                                                                                                        | IDSS                                                 | _                              | _                | 5.0         | mAdc |

| Gate-Body Leakage Current<br>(V <sub>GS</sub> = 20 V, V <sub>DS</sub> = 0)                                                                                   | IGSS                                                 | _                              | -                | 1.0         | μAdc |

| ON CHARACTERISTICS                                                                                                                                           |                                                      |                                |                  |             |      |

| Gate Threshold Voltage<br>(V <sub>DS</sub> = 10 V, I <sub>D</sub> = 100 mA)                                                                                  | V <sub>GS(th)</sub>                                  | 1.0                            | 3.0              | 5.0         | Vdc  |

| Drain-Source On-Voltage<br>((V <sub>G</sub> S = 10 V, I <sub>D</sub> = 10 A)                                                                                 | V <sub>DS(on)</sub>                                  | _                              | _                | 5.0         | Vdc  |

| Forward Transconductance<br>(V <sub>DS</sub> = 10 V, I <sub>D</sub> = 5.0 A)                                                                                 | 9fs                                                  | 4.0                            | 5.0              | _           | mhos |

| DYNAMIC CHARACTERISTICS                                                                                                                                      | •                                                    |                                |                  | 1           |      |

| Input Capacitance<br>(V <sub>DS</sub> = 50 V, V <sub>GS</sub> = 0 V, f = 1.0 MHz)                                                                            | C <sub>iss</sub>                                     | _                              | 350              | -           | pF   |

| Output Capacitance<br>(V <sub>DS</sub> = 50 V, V <sub>GS</sub> = 0, f = 1.0 MHz)                                                                             | C <sub>oss</sub>                                     | _                              | 250              | -           | pF   |

| Reverse Transfer Capacitance<br>(V <sub>DS</sub> = 50 V, V <sub>GS</sub> = 0, f = 1.0 MHz)                                                                   | C <sub>rss</sub>                                     | _                              | 50               | -           | pF   |

| FUNCTIONAL TESTS (SSB)                                                                                                                                       |                                                      | ·                              |                  |             |      |

| Common Source Amplifier Power Gain<br>(V <sub>DD</sub> = 50 V, P <sub>Out</sub> = 150 W (PEP), I <sub>DQ</sub> = 250 mA)                                     | G <sub>ps</sub>                                      | _                              | 17<br>8.0        | _           | dB   |

| Drain Efficiency<br>(V <sub>DD</sub> = 50 V, P <sub>out</sub> = 150 W (PEP), f = 30; 30.001 MHz,<br>I <sub>D</sub> (Max) = 3.75 A)                           | η                                                    | _                              | 45               | _           | %    |

| Intermodulation Distortion (1)<br>(V <sub>DD</sub> = 50 V, P <sub>Out</sub> = 150 W (PEP), f1 = 30 MHz,<br>f2 = 30.001 MHz, I <sub>DQ</sub> = 250 mA)        | IMD <sub>(d3)</sub>                                  |                                | -32<br>-60       | _           | dB   |

| Load Mismatch<br>(V <sub>DD</sub> = 50 V, P <sub>out</sub> = 150 W (PEP), f = 30; 30.001 MHz,<br>I <sub>DQ</sub> = 250 mA, VSWR 30:1 at all Phase Angles)    | Ų                                                    | No Degradation in Output Power |                  |             |      |

| CLASS A PERFORMANCE                                                                                                                                          |                                                      |                                |                  |             |      |

| Intermodulation Distortion (1) and Power Gain (V <sub>DD</sub> = 50 V, P <sub>out</sub> = 50 W (PEP), f1 = 30 MHz, f2 = 30.001 MHz, I <sub>DQ</sub> = 3.0 A) | GPS<br>IMD <sub>(d3)</sub><br>IMD <sub>(d9-13)</sub> |                                | 20<br>-50<br>-75 |             | dB   |

|                                                                                                                                                              |                                                      |                                |                  | <del></del> |      |

<sup>(1)</sup> To MIL-STD-1311 Version A, Test Method 2204B, Two Tone, Reference Each Tone.

#### FIGURE 1 - 30 MHz TEST CIRCUIT (CLASS AB)

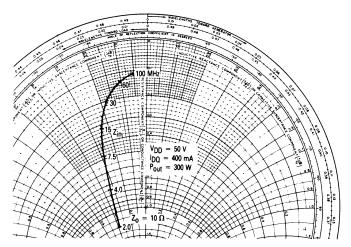

FIGURE 7 - SERIES EQUIVALENT IMPEDANCE

FIGURE 8 - 150 MHz TEST CIRCUIT (CLASS AB)

- C1, C2, C8 Arco 463 or equivalent

- C3 25 pF Unelco

- C4 0.1  $\mu$ F Ceramic

- $C5-1.0~\mu F$ , 15 WV Tantalum

- C6 250 pF Unelco J101

- C7 25 µF Unelco J101

- ${

m C9-Arco~262}$  or equivalent

- ${\rm C10-0.05~\mu F~Ceramic}$

- $C11-15 \mu \dot{F}$ , 60 WV Electrolytic

- D1 1N5347 Zener Diode

- L1 3/4" #18 AWG into Hairpin

- L2 Printed Line, 0.200" × 0.500"

- L3 1" #16 AWG into Hairpin

- $\rm L4-2$  Turns #16 AWG, 5/16 ID

- RFC1 5.6  $\mu$ H Choke

- RFC2 VK200-4B

- R1, R2 150  $\Omega$ , 1.0 W Carbon

#### MOSFET CAPACITANCES

The physical structure of a MOSFET results in capacitors between the terminals. The metal oxide gate structure determines the capacitors from gate-to-drain (Cgd), and gate-to-source (Cgs). The PN junction formed during the fabrication of the TMOS FET results in a junction capacitance from drain-to-source (Cds).

These capacitances are characterized as input  $(C_{iss})$ , output  $(C_{oss})$  and reverse transfer  $(C_{rss})$  capacitances on data sheets. The relationships between the interterminal capacitances and those given on data sheets are shown below. The  $C_{iss}$  can be specified in two ways:

- Drain shorted to source and positive voltage at the gate.

- Positive voltage of the drain in respect to source and zero volts at the gate. In the latter case the numbers are lower. However, neither method represents the actual operating conditions in RF applications.

#### LINEARITY AND GAIN CHARACTERISTICS

In addition to the typical IMD and power gain data presented, Figure 5 may give the designer additional information on the capabilities of this device. The graph represents the small signal unity current gain frequency at a given drain current level. This is equivalent to f $\uptau$  for bipolar transistors. Since this test is performed at a fast sweep speed, heating of the device does not occur. Thus, in normal use, the higher temperatures may degrade these characteristics to some extent.

#### **DRAIN CHARACTERISTICS**

One figure of merit for a FET is its static resistance in the full-on condition. This on-resistance,  $V_{DS(On)}$ , occurs in the linear region of the output characteristic and is specified under specific test conditions for gate-source voltage and drain current. For MOSFETs,  $V_{DS(On)}$  has a positive temperature coefficient and constitutes an important design consideration at high temperatures, because it contributes to the power dissipation within the device.

#### **GATE CHARACTERISTICS**

The gate of the TMOS FET is a polysilicon material, and is electrically isolated from the source by a layer of oxide. The input resistance is very high — on the order of  $10^9$  ohms — resulting in a leakage current of a few nanoamperes.

Gate control is achieved by applying a positive voltage slightly in excess of the gate-to-source threshold voltage, VGS(th).

Gate Voltage Rating — Never exceed the gate voltage rating. Exceeding the rated VGS can result in permanent damage to the oxide layer in the gate region.

**Gate Termination** — The gates of these devices are essentially capacitors. Circuits that leave the gate open-circuited or floating should be avoided. These conditions can result in turn-on of the devices due to voltage build-up on the input capacitor due to leakage currents or pickup.

Gate Protection — These devices do not have an internal monolithic zener diode from gate-to-source. If gate protection is required, an external zener diode is recommended.

## **EQUIVALENT TRANSISTOR PARAMETER TERMINOLOGY**

|                  | 0 - 1 -               |

|------------------|-----------------------|

|                  |                       |

| Emitter          | <br>Source            |

| Base             | <br>Gate              |

| V(BR)CES         | <br>V(BR)DSS          |

| V <sub>СВО</sub> | <br>V <sub>D</sub> GO |

|                  |                       |

|                  |                       |

|                  |                       |

|                  |                       |

|                  |                       |

|                  |                       |

| C <sub>ob</sub>  | <br>Coss              |

| hfe              |                       |

| VCE(sat)         | VDS(on)               |

| RCE(sat) = IC    | <br>IDS(on) - ID      |

# MOTOROLA SEMICONDUCTOR I TECHNICAL DATA

# The RF TMOS Line Power Field Effect Transistor

N-Channel Enhancement Mode TMOS RF

... designed primarily for linear large-signal output stages in the 2-100 MHz frequency range.

Specified 50 Volts, 30 MHz Characteristics

Output Power = 300 Watts

Power Gain = 17 dB (Typ)

Efficiency = 45% (Typ)

TMOS LINEAR RF POWER FETS 300 WATTS 2-100 MHz

#### **MAXIMUM RATINGS**

| Rating                                                                      | Symbol           | Value       | Unit          |

|-----------------------------------------------------------------------------|------------------|-------------|---------------|

| Drain-Source Voltage                                                        | V <sub>DSS</sub> | 125         | Vdc           |

| Drain-Gate Voltage                                                          | V <sub>DGO</sub> | 125         | Vdc           |

| Gate-Source Voltage                                                         | V <sub>GS</sub>  | ±40         | Vdc           |

| Drain Current — Continuous                                                  | ID               | 40          | Adc           |

| Total Device Dissipation $@T_C = 25^{\circ}C$<br>Derate above $25^{\circ}C$ | P <sub>D</sub>   | 700<br>4    | Watts<br>W/°C |

| Storage Temperature Range                                                   | T <sub>stg</sub> | -65 to +150 | ′ ℃           |

| Operating Junction Temperature                                              | TJ               | 200         | °C            |

## THERMAL CHARACTERISTICS

| Characteristic                       | Symbol            | Max  | Unit |

|--------------------------------------|-------------------|------|------|

| Thermal Resistance, Junction to Case | R <sub>Ø</sub> JC | 0.25 | °C/W |

Handling and Packaging — MOS devices are susceptible to damage from electrostatic charge. Reasonable precautions in handling and packaging MOS devices should be observed.

## **MRF153**

#### **ELECTRICAL CHARACTERISTICS** (T<sub>C</sub> = 25°C unless otherwise noted)

| Characteristic                                                                                                                                                         | Symbol               | Min | Тур  | Max | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|------|-----|------|

| OFF CHARACTERISTICS                                                                                                                                                    |                      |     |      |     |      |

| Drain-Source Breakdown Voltage<br>(VGS = 0, I <sub>D</sub> = 100 mA)                                                                                                   | V <sub>(BR)DSS</sub> | 125 | _    | _   | Vdc  |

| Zero Gate Voltage Drain Current (V <sub>DS</sub> = 50 V, ♥ <sub>GS</sub> = 0)                                                                                          | IDSS                 | _   | _    | 10  | mAdc |

| Gate-Body Leakage Current<br>(VGS = 20 V, VDS = 0)                                                                                                                     | l <sub>GSS</sub>     | _   | _    | 3   | μAdc |

| ON CHARACTERISTICS                                                                                                                                                     |                      |     |      |     |      |

| Gate Threshold Voltage<br>(V <sub>DS</sub> = 10 V, I <sub>D</sub> = 100 mA)                                                                                            | V <sub>GS(th)</sub>  | 1   | 3    | 5   | Vdc  |

| Drain-Source On-Voltage<br>(VGS = 10 V, ID = 20 A)                                                                                                                     | V <sub>DS(on)</sub>  | _   | _    | 5   | Vdc  |

| Forward Transconductance<br>(V <sub>DS</sub> = 10 V, I <sub>D</sub> = 10 A)                                                                                            | 9fs                  | 8   | 10   |     | mhos |

| DYNAMIC CHARACTERISTICS                                                                                                                                                |                      |     |      |     |      |

| Input Capacitance<br>(Vps = 50 V, V <sub>GS</sub> = 0 V, f = 1 MHz)                                                                                                    | C <sub>iss</sub>     |     | 800  | _   | pF   |

| Output Capacitance<br>(Vps = 50 V, V <sub>GS</sub> = 0, f = 1 MHz)                                                                                                     | C <sub>oss</sub>     | _   | 500  | _   | pF   |

| Reverse Transfer Capacitance<br>(VDS = 50 V, VGS = 0, f = 1 MHz)                                                                                                       | C <sub>rss</sub>     | _   | 100  | _   | pF   |

| FUNCTIONAL TESTS                                                                                                                                                       |                      |     | _    |     |      |

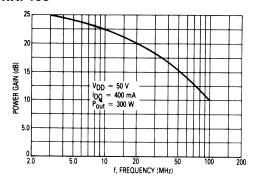

| Common Source Amplifier Power Gain<br>(V <sub>DD</sub> = 50 V, P <sub>Out</sub> = 300 W, I <sub>DQ</sub> = 400 mA)                                                     | G <sub>ps</sub>      | _   | 17   | _   | dB   |

| Drain Efficiency<br>(VDD = 50 V, Pout = 300 W, f = 30 MHz)                                                                                                             | η                    | _   | 45   | _   | %    |

| Intermodulation Distortion ( $V_{DD} = 50 \text{ V}$ , $P_{Out} = 300 \text{ W}(PEP)$ , $f1 = 30 \text{ MHz}$ , $f2 = 30.001 \text{ MHz}$ , $I_{DQ} = 40 \text{ mA}$ ) | IMD <sub>(d3)</sub>  | _   | - 25 | _   | dB   |

All capacitors ATC type 100/200 chips or equivalent unless otherwise noted.

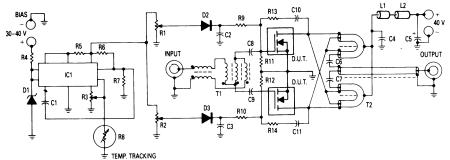

Figure 1. 30 MHz Test Circuit

## **MRF153**

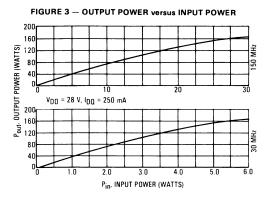

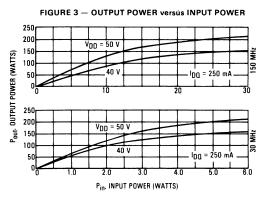

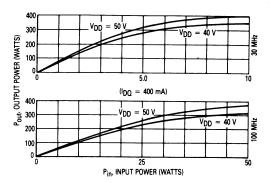

Figure 3. Output Power versus Input Power

Figure 4. Series Equivalent Impedance

- C1 1000 pF Ceramic C2. C3. C4. C8. C9, C10, C11 0.1  $\mu$ F Ceramic

- C5 10 μF/100 V Electrolytic

- C6, C7 0.1  $\mu$ F Ceramic, (ATC 200/823 or Equivalent) D1 28 V Zener, 1N5362 or Equivalent . D3 1N4148

- IC1 MC1723

- L1, L2 Fair-Rite Products Corp. Ferrite Beads #2673000801 R1, R2, R3 10 k Trimpot R4 1.0 k / 1.0 W

- R6 2.0 k

- R5 10 Ohms

- R7 10 k R8 Thermistor, 10 k (25°C), 2.5 k (75°C) R9, R10 100 Ohms R11, R12 1.0 k

- R13, R14 50–100 Ohms, 4 x 2 W Carbon in Parallel

T1 9:1 Transformer, Trifilar and Balun Wound on Separate

Fair-Rite Products Corp. Balun Cores #286100012, 5 Turns Each.

- T2 1:9 Transformer, Balun 50 Ohm CO-AX Cable RG-188, Low Impedance Lines W.L. Gore 16 Ohms CO-AX Type CXN 1837. Each Winding Threaded Through Two Fair-Rite Products Corp. #2661540001 Ferrite Sleeves (6 Each).

Figure 5. 20-80 MHz 500 W Broadband Amplifier

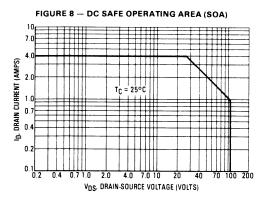

Figure 6. DC Safe Operating Area

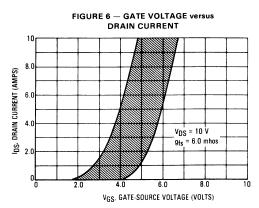

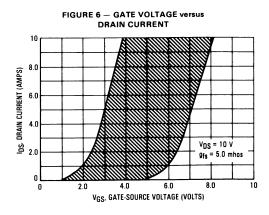

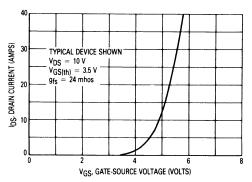

Figure 8. Gate Voltage versus Drain Current

Figure 7. Capacitance versus Drain Voltage

Figure 9. Common Source Unity Gain Frequency versus Drain Current

#### **MOSFET CAPACITANCES**

The physical structure of a MOSFET results in capacitors between the terminals. The metal oxide gate structure determines the capacitors from gate-to-drain ( $C_{\rm gd}$ ), and gate-to-source ( $C_{\rm gs}$ ). The PN junction formed during the fabrication of the TMOS FET results in a junction capacitance from drain-to-source ( $C_{\rm ds}$ ).

These capacitances are characterized as input  $(C_{iss})$ , output  $(C_{oss})$  and reverse transfer  $(C_{rss})$  capacitances on data sheets. The relationships between the interterminal capacitances and those given on data sheets are shown below. The  $C_{iss}$  can be specified in two ways:

- Drain shorted to source and positive voltage at the gate.

- Positive voltage of the drain in respect to source and zero volts at the gate. In the latter case the numbers are lower. However, neither method represents the actual operating conditions in RF applications.

#### LINEARITY AND GAIN CHARACTERISTICS

In addition to the typical IMD and power gain data presented, Figure 5 may give the designer additional information on the capabilities of this device. The graph represents the small signal unity current gain frequency at a given drain current level. This is equivalent to ft for bipolar transistors. Since this test is performed at a fast sweep speed, heating of the device does not occur. Thus, in normal use, the higher temperatures may degrade these characteristics to some extent.

#### **DRAIN CHARACTERISTICS**

One figure of merit for a FET is its static resistance in the full-on condition. This on-resistance, V<sub>DS(on)</sub>, occurs in the linear region of the output characteristic and is specified under specific test conditions for gate-source voltage and drain current. For MOSFETs, V<sub>DS(on)</sub> has a positive temperature coefficient and constitutes an important design consideration at high temperatures, because it contributes to the power dissipation within the device.

#### **GATE CHARACTERISTICS**

The gate of the TMOS FET is a polysilicon material, and is electrically isolated from the source by a layer of oxide. The input resistance is very high — on the order of 109 ohms — resulting in a leakage current of a few nanoamperes.

Gate control is achieved by applying a positive voltage slightly in excess of the gate-to-source threshold voltage,

**Gate Voltage Rating** — Never exceed the gate voltage rating. Exceeding the rated  $V_{GS}$  can result in permanent damage to the oxide layer in the gate region.

Gate Termination — The gates of these devices are essentially capacitors. Circuits that leave the gate open-circuited or floating should be avoided. These conditions can result in turn-on of the devices due to voltage build-up on the input capacitor due to leakage currents or pickup.

**Gate Protection** — These devices do not have an internal monolithic zener diode from gate-to-source. The addition of an internal zener diode may result in detrimental effects on the reliability of a power MOSFET. If gate protection is required, an external zener diode is recommended.

## MOUNTING OF HIGH POWER RF POWER TRANSISTORS

The package of this device is designed for conduction cooling. It is extremely important to minimize the thermal resistance between the device flange and the heat dissipator.

Since the device mounting flange is made of soft copper, it may be deformed during various stages of handling or during transportation. It is recommended that the user makes a final inspection on this before the device installation.  $\pm 0.0005^{\prime\prime}$  is considered sufficient for the flange bottom.

The same applies to the heat dissipator in the device mounting area. If copper heatsink is not used, a copper head spreader is strongly recommended between the device mounting surfaces and the main heatsink. It should be at least 1/4" thick and extend at least one inch from the flange edges. A thin layer of thermal compound in all interfaces is, of course, essential. The recommended torque on the 4-40 mounting screws should be in the area of 4–5 lbs.-inch, and spring type lock washers along with flat washers are recommended.

For die temperature calculations, the  $\Delta$  temperature from a corner mounting screw area to the bottom center of the flange is approximately 5°C and 10°C under normal operating conditions (dissipation 150 W and 300 W respectively).

The main heat dissipator must be sufficiently large and have low  $R_{\theta}$  for moderate air velocity, unless liquid cooling is employed.

#### CIRCUIT CONSIDERATIONS

At high power levels (500 W and up), the circuit layout becomes critical due to the low impedance levels and high RF currents associated with the output matching. Some of the components, such as capacitors and inductors must also withstand these currents. The component losses are directly proportional to the operating frequency. The manufacturers specifications on capacitor ratings should be consulted on these aspects prior to design.

Push-pull circuits are less critical in general, since the ground referenced RF loops are practically eliminated,

and the impedance levels are higher for a given power output. High power broadband transformers are also easier to design than comparable LC matching networks.

## **EQUIVALENT TRANSISTOR PARAMETER TERMINOLOGY**

| Collector<br>Emitter<br>Base              |                                             |

|-------------------------------------------|---------------------------------------------|

| V(BR)CES<br>VCBO                          | <br>V(BR)DSS                                |

| ICES                                      | <br>                                        |

| IEBO<br>VBE(on)                           | <br>IGSS                                    |

| VCE(sat)                                  | <br>VDS(on)                                 |

| C <sub>ob</sub>                           | <br>9fs                                     |

| $R_{CE(sat)} = \frac{V_{CE(sat)}}{I_{C}}$ | <br>$r_{DS(on)} = \frac{V_{DS(on)}}{I_{D}}$ |

# MOTOROLA SEMICONDUCTOR I TECHNICAL DATA

The RF TMOS Line

Power Field Effect Transistor

N-Channel Enhancement Mode TMOS RF

... designed primarily for linear large-signal output stages in the 2-100 MHz frequency range.

Specified 50 Volts, 30 MHz Characteristics

Output Power = 600 Watts

Power Gain = 17 dB (Typ)

Efficiency = 45% (Typ)

**MRF154**

TMOS LINEAR RF POWER FETS 600 WATTS 2-100 MHz

#### **MAXIMUM RATINGS**

| Rating                                                                | Symbol           | Value       | Unit          |

|-----------------------------------------------------------------------|------------------|-------------|---------------|

| Drain-Source Voltage                                                  | V <sub>DSS</sub> | 125         | Vdc           |

| Drain-Gate Voltage                                                    | V <sub>DGO</sub> | 125         | Vdc           |

| Gate-Source Voltage                                                   | V <sub>GS</sub>  | ± 40        | Vdc           |

| Drain Current — Continuous                                            | ID               | 60          | Adc           |

| Total Device Dissipation @ T <sub>C</sub> = 25°C<br>Derate above 25°C | PD               | 1350<br>7.7 | Watts<br>W/°C |

| Storage Temperature Range                                             | T <sub>stq</sub> | -65 to +150 | , c           |

| Operating Junction Temperature                                        | Tj               | 200         | °C            |

## THERMAL CHARACTERISTICS

| Characteristic                       | Symbol | Max  | Unit |

|--------------------------------------|--------|------|------|

| Thermal Resistance, Junction to Case | RøJC   | 0.13 | °C/W |

Handling and Packaging — MOS devices are susceptible to damage from electrostatic charge. Reasonable precautions in handling and packaging MOS devices should be observed.

## **MRF154**

### **ELECTRICAL CHARACTERISTICS** (T<sub>C</sub> = 25°C unless otherwise noted)

| Characteristic                                                                                                                                   | Symbol                | Min | Тур  | Max | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|------|-----|------|

| OFF CHARACTERISTICS                                                                                                                              |                       |     |      |     |      |

| Drain-Source Breakdown Voltage<br>(V <sub>GS</sub> = 0, I <sub>D</sub> = 100 mA)                                                                 | V <sub>(BR)</sub> DSS | 125 | _    |     | Vdc  |

| Zero Gate Voltage Drain Current<br>(VDS = 50 V, VGS = 0)                                                                                         | IDSS                  |     | _    | 20  | mAdc |

| Gate-Body Leakage Current<br>(VGS = 20 V, VDS = 0)                                                                                               | <sup>I</sup> GSS      | _   | _    | 5   | μAdc |

| ON CHARACTERISTICS                                                                                                                               |                       |     |      |     |      |

| Gate Threshold Voltage<br>(V <sub>DS</sub> = 10 V, I <sub>D</sub> = 100 mA)                                                                      | V <sub>GS(th)</sub>   | 1   | 3    | 5   | Vdc  |

| Drain-Source On-Voltage<br>(V <sub>GS</sub> = 10 V, I <sub>D</sub> = 40 A)                                                                       | V <sub>DS(on)</sub>   |     | _    | 5   | Vdc  |

| Forward Transconductance<br>(V <sub>DS</sub> = 10 V, I <sub>D</sub> = 20 A)                                                                      | 9fs                   | 16  | 20   |     | mhos |

| DYNAMIC CHARACTERISTICS                                                                                                                          |                       |     |      |     |      |

| Input Capacitance $(V_{DS} = 50 \text{ V, } V_{GS} = 0 \text{ V, } f = 1 \text{ MHz})$                                                           | C <sub>iss</sub>      |     | 1600 | _   | pF   |

| Output Capacitance<br>(V <sub>DS</sub> = 50 V, V <sub>GS</sub> = 0, f = 1 MHz)                                                                   | C <sub>oss</sub>      | _   | 1000 | _   | pF   |

| Reverse Transfer Capacitance<br>(V <sub>DS</sub> = 50 V, V <sub>GS</sub> = 0, f = 1 MHz)                                                         | C <sub>rss</sub>      | _   | 200  |     | pF   |

| FUNCTIONAL TESTS                                                                                                                                 |                       |     |      |     |      |

| Common Source Amplifier Power Gain $(V_{DD} = 50 \text{ V}, P_{out} = 600 \text{ W}, I_{DQ} = 800 \text{ mA}, f = 30 \text{ MHz})$               | G <sub>ps</sub>       | _   | 17   | _   | dB   |

| Drain Efficiency $(V_{DD} = 50 \text{ V}, P_{out} = 600 \text{ W}, I_{DQ} = 800 \text{ mA}, f = 30 \text{ MHz})$                                 | η                     | _   | 45   | _   | %    |

| Intermodulation Distortion<br>(V <sub>DD</sub> = 50 V, P <sub>Out</sub> = 600 W(PEP), f1 = 30 MHz,<br>f2 = 30.001 MHz, I <sub>DQ</sub> = 800 mA) | IMD(d3)               | _   | - 25 | _   | dB   |

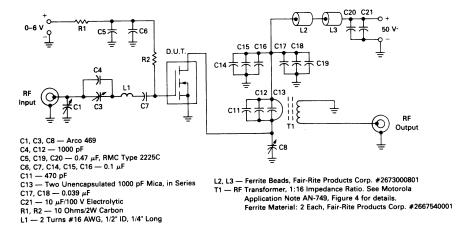

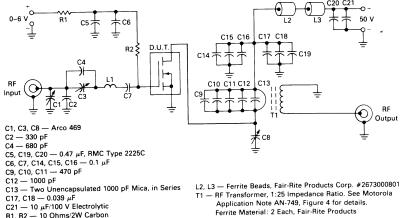

R1, R2 — 10 Ohms/2W Carbon

L1 — 2 Turns #16 AWG, 1/2" ID, 3/8" Long

T1 — RF Transformer, 1:25 Impedance Ratio. See Motorola Application Note AN-749, Figure 4 for details. Ferrite Material: 2 Each, Fair-Rite Products Corp. #2667540001

All capacitors ATC type 100/200 chips or equivalent unless otherwise noted.

FIGURE 1 — 30 MHz TEST CIRCUIT

## **MRF154**

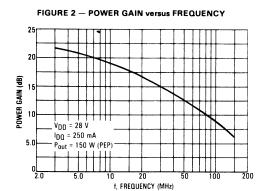

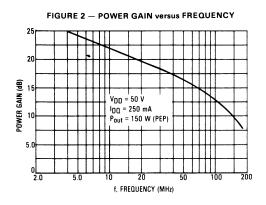

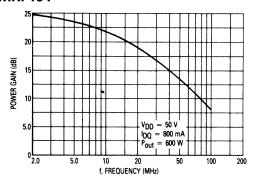

Figure 2. Power Gain versus Frequency

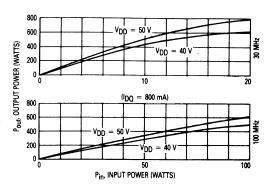

Figure 3. Output Power versus Input Power

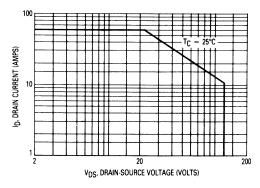

Figure 4. DC Safe Operating Area

Figure 5. Capacitance versus Drain Voltage

Figure 6. Gate Voltage versus Drain Current

Figure 7. Common Source Unity Gain Frequency versus Drain Current

Figure 8. Series Equivalent Impedance

R9

C10

R13

Figure 9. 20-80 MHz 1 kW Broadband Amplifier

#### MOSFET CAPACITANCES

The physical structure of a MOSFET results in capacitors between the terminals. The metal oxide gate structure determines the capacitors from gate-to-drain (Cgd), and gate-to-source (Cgs). The PN junction formed during the fabrication of the TMOS FET results in a junction capacitance from drain-to-source (Cds).

These capacitances are characterized as input  $(C_{iss})$ , output  $(C_{Oss})$  and reverse transfer  $(C_{rss})$  capacitances on data sheets. The relationships between the interterminal capacitances and those given on data sheets are shown below. The  $C_{iss}$  can be specified in two ways:

- Drain shorted to source and positive voltage at the gate.

- Positive voltage of the drain in respect to source and zero volts at the gate. In the latter case the numbers are lower. However, neither method represents the actual operating conditions in RF applications.

#### LINEARITY AND GAIN CHARACTERISTICS

In addition to the typical IMD and power gain data presented, Figure 5 may give the designer additional information on the capabilities of this device. The graph represents the small signal unity current gain frequency at a given drain current level. This is equivalent to f7 for bipolar transistors. Since this test is performed at a fast sweep speed, heating of the device does not occur. Thus, in normal use, the higher temperatures may degrade these characteristics to some extent.

## **DRAIN CHARACTERISTICS**

One figure of merit for a FET is its static resistance in the full-on condition. This on-resistance, V<sub>DS(on)</sub>, occurs in the linear region of the output characteristic and is specified under specific test conditions for gate-source voltage and drain current. For MOSFETs, V<sub>DS(on)</sub> has a positive temperature coefficient and constitutes an important design consideration at high temperatures, because it contributes to the power dissipation within the device.

#### **GATE CHARACTERISTICS**

The gate of the TMOS FET is a polysilicon material, and is electrically isolated from the source by a layer of

oxide. The input resistance is very high — on the order of  $10^9$  ohms — resulting in a leakage current of a few nanoamperes.

Gate control is achieved by applying a positive voltage slightly in excess of the gate-to-source threshold voltage, VGS(th).

**Gate Voltage Rating** — Never exceed the gate voltage rating. Exceeding the rated  $V_{GS}$  can result in permanent damage to the oxide layer in the gate region.

Gate Termination — The gates of these devices are essentially capacitors. Circuits that leave the gate open-circuited or floating should be avoided. These conditions can result in turn-on of the devices due to voltage build-up on the input capacitor due to leakage currents or pickup.

Gate Protection — These devices do not have an internal monolithic zener diode from gate-to-source. The addition of an internal zener diode may result in detrimental effects on the reliability of a power MOSFET. If gate protection is required, an external zener diode is recommended.

#### MOUNTING OF HIGH POWER RF POWER TRANSISTORS

The package of this device is designed for conduction cooling. It is extremely important to minimize the thermal resistance between the device flange and the heat dissipator.

Since the device mounting flange is made of soft copper, it may be deformed during various stages of handling or during transportation. It is recommended that the user makes a final inspection on this before the device installation.  $\pm 0.0005''$  is considered sufficient for the flange bottom.

The same applies to the heat dissipator in the device mounting area. If copper heatsink is not used, a copper head spreader is strongly recommended between the device mounting surfaces and the main heatsink. It should be at least 1/4" thick and extend at least one inch from the flange edges. A thin layer of thermal compound in all interfaces is, of course, essential. The recommended torque on the 4-40 mounting screws should be in the area of 4-5 lbs.-inch, and spring type lock washers along with flat washers are recommended.

For die temperature calculations, the  $\Delta$  temperature from a corner mounting screw area to the bottom center of the flange is approximately 5°C and 10°C under normal operating conditions (dissipation 150 W and 300 W respectively).

The main heat dissipator must be sufficiently large and have low  $R_{\theta}$  for moderate air velocity, unless liquid cooling is employed.

## CIRCUIT CONSIDERATIONS

At high power levels (500 W and up), the circuit layout becomes critical due to the low impedance levels and high RF currents associated with the output matching. Some of the components, such as capacitors and inductors must also withstand these currents. The component losses are directly proportional to the operating frequency. The manufacturers specifications on capacitor ratings should be consulted on these aspects prior to design.

Push-pull circuits are less critical in general, since the ground referenced RF loops are practically eliminated, and the impedance levels are higher for a given power output. High power broadband transformers are also easier to design than comparable LC matching networks.

## **EQUIVALENT TRANSISTOR PARAMETER TERMINOLOGY**

| Collector            | <br>Drain                              |

|----------------------|----------------------------------------|

| Emitter              | <br>Source                             |

| Base                 | <br>Gate                               |

| V(BR)CES             |                                        |

| Vcво                 | <br>$V_{DGO}$                          |

| lc                   | <br>lD D                               |

| ICES                 | <br>DSS                                |

| I <sub>EBO</sub>     | <br>IGSS                               |

| V <sub>BE(on)</sub>  | <br>VGS(th)                            |

| V <sub>CE(sat)</sub> | <br>V <sub>DS(on)</sub>                |

| Cib                  | <br>C <sub>iss</sub>                   |

| Cob                  | <br>Coss                               |

| h <sub>fe</sub>      | <br>9fs                                |

| V <sub>CE(sat)</sub> | <br>$r_{DS(on)} = \frac{V_{DS(on)}}{}$ |

| RCE(sat) = IC        | $rDS(on) = \frac{1}{D}$                |

#### **OUTLINE DIMENSIONS**

2