# MTM814, MTM815 MTP814, MTP815

# Designer's Data Sheet

#### P-CHANNEL ENHANCEMENT MODE SILICON GATE TMOS POWER FIELD EFFECT TRANSISTOR

These TMOS Power FETs are designed for medium voltage, high speed power switching applications such as switching regulators, converters, solenoid and relay drivers.

- Silicon Gate for Fast Switching Speeds Switching Times Specified at 100°C

- Designers Data I<sub>DSS</sub>, V<sub>DS(on)</sub> and SOA Specified at Elevated Temperature

- Rugged SOA is Power Dissipation Limited

- Source to Drain Diode Characterized for Use With Inductive Loads

- Low Drive Requirement, VG(th) = 4.0 Volts (max)

#### **MAXIMUM RATINGS**

| Rating                                                            | Symbol                            | MTM814<br>MTP814 | MTM815<br>MTP815 | Unit          |

|-------------------------------------------------------------------|-----------------------------------|------------------|------------------|---------------|

| Drain — Source Voltage                                            | V <sub>DSS</sub>                  | 80               | 100              | Vdc           |

| Drain — Gate Voltage                                              | V <sub>DGO</sub>                  | 80               | 100              | Vdc           |

| Gate — Source Voltage                                             | V <sub>G</sub> S                  | ±                | 20               | Vdc           |

| Drain Current<br>Continuous<br>Pulsed                             | I <sub>D</sub>                    | 8.0<br>20        |                  | Adc           |

| Gate Current — Pulsed                                             | <sup>I</sup> GM                   | 1.5              |                  | Adc           |

| Total Power Dissipation @ T <sub>C</sub> = 25°C Derate above 25°C | PD                                | 75<br>0.6        |                  | Watts<br>W/°C |

| Operating and Storage<br>Temperature Range                        | T <sub>J</sub> , T <sub>stg</sub> | -65 to 150       |                  | °C            |

#### THERMAL CHARACTERISTICS

| Thermal Resistance Junction to Case                                           | $R_{	heta JC}$ | 1.67 | °C/W |

|-------------------------------------------------------------------------------|----------------|------|------|

| Maximum Lead Temp. for<br>Soldering Purposes, 1/8"<br>from case for 5 seconds | ΤL             | 275  | °C   |

#### Designer's Data for "Worst Case" Conditions

The Designer's Data Sheet permits the design of most circuits entirely from the information presented. Limit data — representing device characteristics boundaries — are given to facilitate "worst case" design.

#### **8 AMPERE**

#### P-CHANNEL TMOS POWER FET

80 and 100 VOLTS

### ELECTRICAL CHARACTERISTICS (T<sub>C</sub> = 25°C unless otherwise noted)

| Chara                                                                                                                                                      | acteristic                                                 | Symbol              | Min         | Max               | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------|-------------|-------------------|------|

| OFF CHARACTERISTICS                                                                                                                                        |                                                            |                     |             |                   |      |

| Drain-Source Breakdown Voltag<br>(VGS = 0, ID = 5.0 mA)                                                                                                    | ge<br>MTM814/MTP814<br>MTM815/MTP815                       | V(BR)DSS            | 80<br>100   | _                 | Vdc  |

| Zero Gate Voltage Drain Curren<br>(VDS = 0.85 BVDSS, VGS = 0<br>TJ = 100°C                                                                                 |                                                            | IDSS                | _           | 0.25<br>2.5       | mAdc |

| Gate-Body Leakage Current<br>(VGS = 20 Vdc, VDS = 0)                                                                                                       |                                                            | <sup>I</sup> GSS    | _           | 500               | nAdc |

| ON CHARACTERISTICS*                                                                                                                                        |                                                            |                     |             |                   |      |

| Gate Threshold Voltage<br>(Ip = 1.0 mA, Vps = Vgs)                                                                                                         |                                                            | VGS(th)             | 1.5         | 4.0               | Vdc  |

| Drain-Source On-Voltage (V <sub>GS</sub><br>(I <sub>D</sub> = 4.0 Adc)<br>(I <sub>D</sub> = 8.0 Adc)<br>(I <sub>D</sub> = 4.0 Adc, T <sub>J</sub> = 100°C) | = 10 V)                                                    | V <sub>DS(on)</sub> | _<br>_<br>_ | 1.6<br>3.2<br>3.0 | Vdc  |

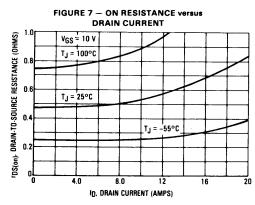

| Static Drain-Source On-Resista<br>(VGS = 10 Vdc, I <sub>D</sub> = 4.0 Adc)                                                                                 | nce                                                        | rDS(on)             | -           | 0.4               | Ohms |

| Forward Transconductance<br>(V <sub>DS</sub> = 15 V, I <sub>D</sub> = 4.0 A)                                                                               |                                                            | 9fs                 | 2.0         | _                 | mhos |

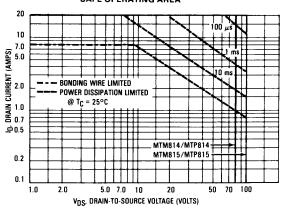

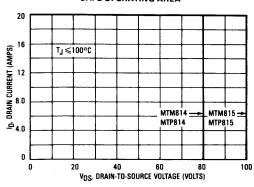

| SAFE OPERATING AREAS                                                                                                                                       |                                                            |                     |             |                   |      |

| Forward Biased Safe Operating                                                                                                                              | Area                                                       | FBSOA               |             | See Figure 13     |      |

| Switching Safe Operating Area                                                                                                                              |                                                            | SSOA                |             | See Figure 14     |      |

| DYNAMIC CHARACTERISTIC                                                                                                                                     | cs                                                         |                     |             |                   |      |

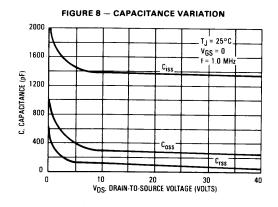

| Input Capacitance                                                                                                                                          |                                                            | C <sub>iss</sub>    | _           | 1200              | pF   |

| Output Capacitance                                                                                                                                         | (V <sub>DS</sub> = 25 V, V <sub>GS</sub> = 0, f = 1.0 MHz) | Coss                | _           | 600               | pF   |

| Reverse Transfer Capacitance                                                                                                                               |                                                            | C <sub>rss</sub>    |             | 180               | рF   |

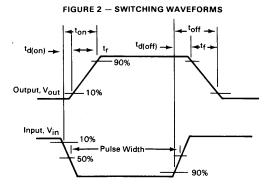

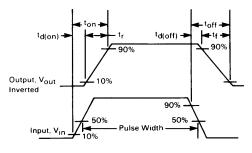

| SWITCHING CHARACTERIST                                                                                                                                     | rics* (T <sub>J</sub> = 100°C)                             |                     |             |                   |      |

| Turn-On Delay Time                                                                                                                                         |                                                            | td(on)              | _           | 80                | ns   |

| Rise Time                                                                                                                                                  | (V <sub>DS</sub> = 25 V, I <sub>D</sub> = 4.0 A,           | t <sub>r</sub>      |             | 150               | ns   |

| Turn-Off Delay Time                                                                                                                                        | R <sub>gen</sub> = 50 ohms)                                | td(off)             | _           | 200               | → ns |

| Fall Time                                                                                                                                                  |                                                            | tf                  |             | 150               | ns   |

| SOURCE DRAIN DIODE CHA                                                                                                                                     | RACTERISTICS*                                              |                     |             |                   |      |

|                       | Characteristic         | Symbol          | Тур | Unit |

|-----------------------|------------------------|-----------------|-----|------|

| Forward On-Voltage    | I <sub>S</sub> = 8.0 A | V <sub>SD</sub> | 1.3 | Vdc  |

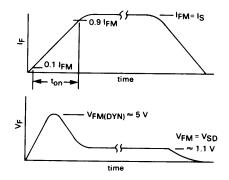

| Forward Turn-On Time  | V <sub>GS</sub> = 0    | ton             | 250 | ns   |

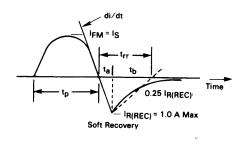

| Reverse Recovery Time | See Figures 17 and 18  | t <sub>rr</sub> | 325 | ns   |

<sup>\*</sup>Pulse Test: Pulse Width ≤300 μs, Duty Cycle ≤2%.

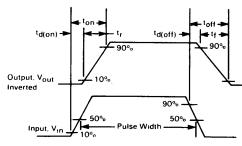

#### **RESISTIVE SWITCHING**

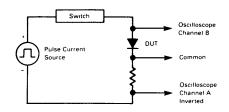

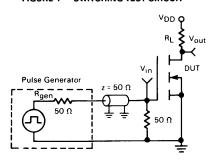

FIGURE 1 — SWITCHING TEST CIRCUIT √

vout DUT **Pulse Generator** 50 Ω

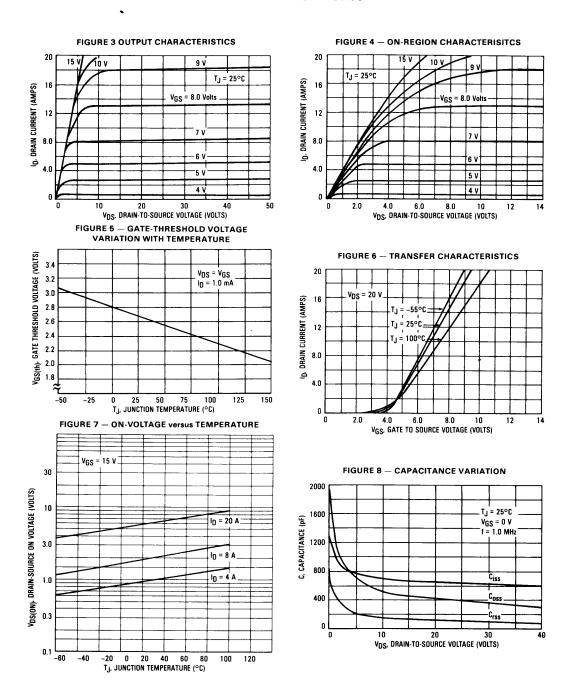

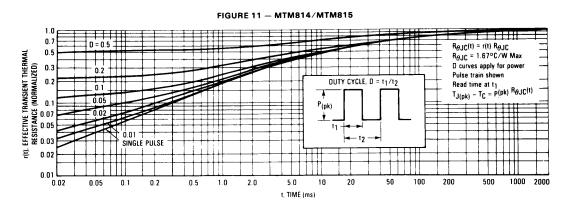

#### **TYPICAL CHARACTERISTICS**

#### TYPICAL CHARACTERISTICS

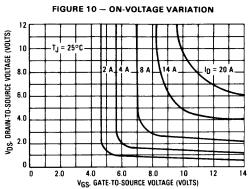

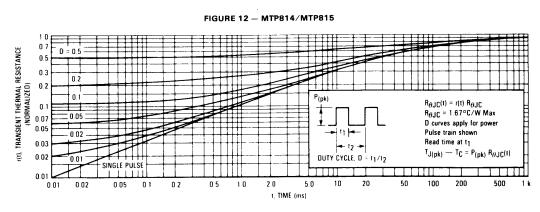

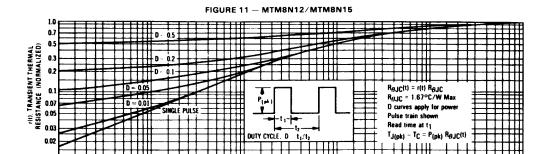

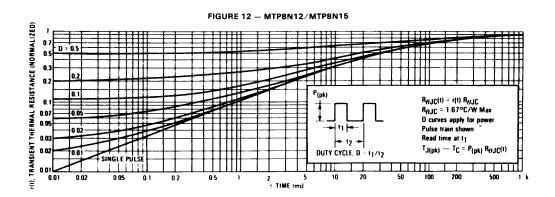

### THERMAL RESPONSE

#### SAFE OPERATING AREA INFORMATION

FIGURE 13 — MAXIMUM FORWARD BIASED SAFE OPERATING AREA

FIGURE 14 — MAXIMUM SWITCHING SAFE OPERATING AREA

#### **FORWARD BIASED**

The data of Figure 13 is based on  $T_C$  = 25°C,  $T_{J(pk)}$  is a variable depending on the power level. The allowable current at the voltages shown in Figure 13 may be calculated for any case temperature with the aid of the following equation:

$$I_D(T_C) = I_D(25^{\circ}C) \left[ 1 - \frac{T_C - 25^{\circ}C}{P_D R_{\theta JC}} \right]$$

where

$ID(T_C)$  = the maximum allowable current at a case temperature,  $T_C$ .

$I_D(25^{\circ}C)$  = the maximum allowable current at a given voltage from Figure 13.

$\begin{array}{ll} P_D & = \text{the rated power dissipation at } T_C = 25^{\circ}C. \\ R_{\theta JC} & = \text{the rated steady state thermal resistance} \end{array}$

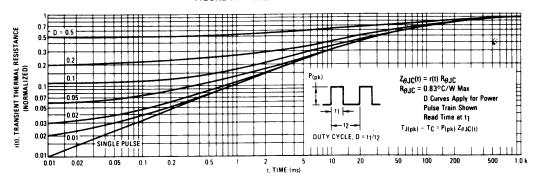

For various pulse widths and duty cycles, substitute  $R_{\theta,JC\{t\}}$  determined from Figures 11 and 12 for  $R_{\theta,JC}$ .

#### SWITCHING SAFE OPERATING AREA

The switching safe operating area (SOA) of Figure 14, is the boundary that the load line may traverse without incurring damage to the MOSFET. The fundamental limits are the peak current, I<sub>DM</sub> and the breakdown voltage, V<sub>(BR)DSS</sub>. The switching SOA shown in Figure 14 is applicable for both turn-on and turn-off of the devices for switching times less than one microsecond.

### TMOS POWER FET CONSIDERATIONS

**Switching Speed** — The switching speeds of these devices are dependent on the driving impedance. Extremely fast switching speeds can be attained by driving the gate from a voltage source.

Transfer Characteristics — The transfer characteristics are linear at drain currents of 500 mA. (See Figure 6.) Linear amplifiers with high frequency response can be designed using this product.

**Gate Voltage Rating** — Never exceed the gate voltage rating of  $\pm 20$  V. Exceeding the rated V<sub>GS</sub> can result in permanent damage to the oxide layer in the gate region.

Gate Termination — The gate of these devices are essentially capacitors. Circuits that leave the gate open-circuited or floating should be avoided. These conditions can result in turn-on of the

devices due to voltage build-up on the input capacitor due to leakage currents or pickup.

Gate Protection — These devices do not have an internal monolithic zener diode from gate to source. The addition of an internal zener diode may result in detrimental effects on the reliability of a power MOSFET. If gate protection is required, an external zener diode is recommended.

Handling and Packaging — MOS ICs are susceptible to damage from electrostatic charge. Experience has shown that these devices are more rugged than MOS ICs. This is primarily due to the comparatively larger capacitances associated with power devices, however, reasonable precautions in handling and packaging MOS devices should be observed.

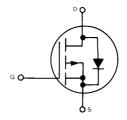

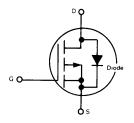

#### TMOS SOURCE TO DRAIN DIODE CHARACTERISTICS

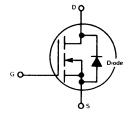

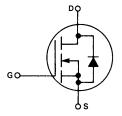

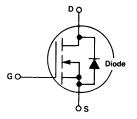

In the fabrication of a TMOS FET, a diode is formed across the source-to-drain terminals as shown in Figure 15. Reversal of the drain voltage will cause current flow in the reverse direction. This

#### FIGURE 15 - TMOS FET WITH **SOURCE-TO-DRAIN DIODE**

diode may be used in circuits requiring external fast recovery diodes, therefore, typical characteristics of the on voltage, forward turn-on and reverse recovery times are given.

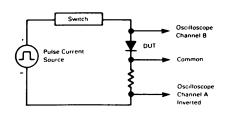

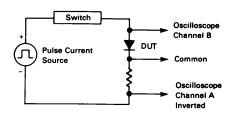

FIGURE 16 — DIODE TURN-ON TEST CIRCUIT

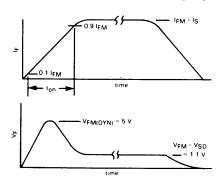

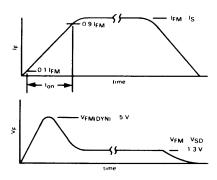

FIGURE 17 — DIODE TURN-ON WAVEFORMS

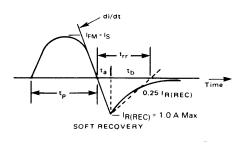

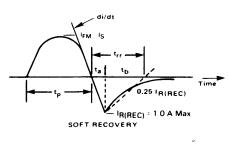

FIGURE 18 - REVERSE RECOVERY CHARACTERISTIC

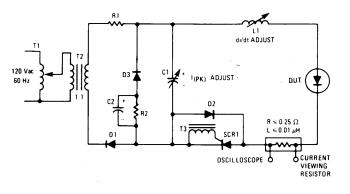

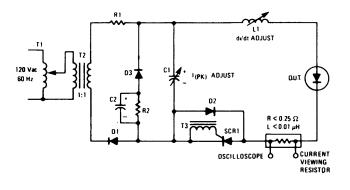

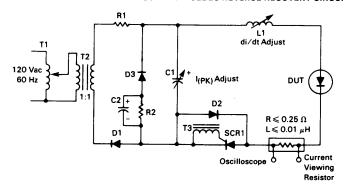

FIGURE 19 - JEDEC REVERSE RECOVERY CIRCUIT

- R1 = 50 Ohms 82 = 250 Ohms

- D1 = 1N4723 D2 = 1N4001

- D3 = 1N4933 SCR1 = MCR729·10 C1 = 0.5 to 50 μF C2 = 4000 µF

- $L1 = 1.0 27 \mu H$ T1 = Variac Adjusts I(PK) and di/dt

- T2 = 1:1

- T3 = 1:1 (to trigger circuit)

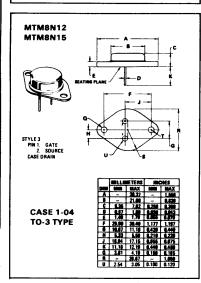

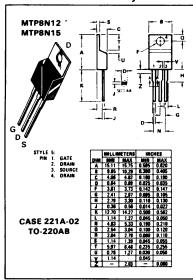

# MTM8N12, MTM8N15 MTP8N12, MTP8N15

## Designer's Data Sheet

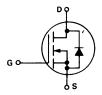

# N-CHANNEL ENHANCEMENT MODE SILICON GATE TMOS POWER FIELD EFFECT TRANSISTOR

These TMOS Power FETs are designed for high voltage, high speed power switching applications such as switching regulators, converters, solenoid and relay drivers.

- Silicon Gate for Fast Switching Speeds Switching Times Specified at 100°C

- Designers Data IDSS, VDS(on) and SOA Specified at Elevated Temperature

- Rugged SOA is Power Dissipation Limited

- Source to Drain Diode Characterized for Use With Inductive Loads

- Low Drive Requirement, VG(th) = 4.5 Volts (max)

#### **MAXIMUM RATINGS**

| Rating                                                            | Symbol               | MTM8N12<br>MTP8N12 | MTM8N15<br>MTP8N15 | Unit          |

|-------------------------------------------------------------------|----------------------|--------------------|--------------------|---------------|

| Drain — Source Voltage                                            | VDSS                 | 120                | 150                | Vdc           |

| Drain — Gate Voltage<br>(RGS = 1 megΩ)                            | V <sub>DGR</sub>     | 120                | 150                | Vdc           |

| Gate — Source Voltage                                             | V <sub>GS</sub>      | ±                  | 20                 | Vdc           |

| Drain Current<br>Continuous<br>Pulsed                             | I <sub>D</sub>       | 8.0<br>20          |                    | Adc           |

| Gate Current — Pulsed                                             | GM                   | 1.5                |                    | Adc           |

| Total Power Dissipation @ T <sub>C</sub> = 25°C Derate above 25°C | PD                   | 75<br>0.6          |                    | Watts<br>W/°C |

| Operating and Storage<br>Temperature Range                        | Tj, T <sub>stg</sub> | -65 to 150         |                    | °C            |

#### THERMAL CHARACTERISTICS

| Thermal Resistance Junction to Case                                           | R <sub>θ</sub> JC | 1.67 | °C/W |

|-------------------------------------------------------------------------------|-------------------|------|------|

| Maximum Lead Temp. for<br>Soldering Purposes, 1/8"<br>from case for 5 seconds | TL                | 275  | °C   |

#### Designer's Data for "Worst Case" Conditions

The Designer's Data Sheet permits the design of most circuits entirely from the information presented. Limit data — representing device characteristics boundaries — are given to facilitate "worst case" design.

#### **8 AMPERE**

#### N-CHANNEL TMOS POWER FET

r<sub>DS(on)</sub> = 0.5 OHMS 120 and 150 VOLTS

| Chara                                                                                                                                                        | cteristic                                                  | Symbol              | Min         | Max               | Unit        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------|-------------|-------------------|-------------|

| OFF CHARACTERISTICS                                                                                                                                          |                                                            |                     |             |                   |             |

| Drain-Source Breakdown Voltag<br>(VGS = 0, ID = 5.0 mA)                                                                                                      | MTM8N12/MTP8N12<br>MTM8N15/MTP8N15                         | V(BR)DSS            | 120<br>150  | =                 | Vdc         |

| Zero Gate Voltage Drain Current<br>(VDS = 0.85 Rated VDSS, VGS<br>TJ = 100°C                                                                                 |                                                            | IDSS                | _           | 0.25<br>2.5       | mAdc        |

| Gate-Body Leakage Current<br>(VGS = 20 Vdc, VDS = 0)                                                                                                         |                                                            | lgss                | _           | 500               | nAdc        |

| ON CHARACTERISTICS*                                                                                                                                          |                                                            |                     |             |                   |             |

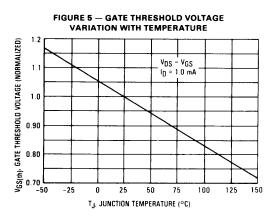

| Gate Threshold Voltage<br>(I <sub>D</sub> = 1.0 mA, V <sub>DS</sub> = V <sub>GS</sub> )<br>T <sub>J</sub> = 100°C                                            |                                                            | VGS(th)             | 2.0<br>1.5  | 4.5<br>4.0        | Vdc         |

| Drain-Source On-Voltage (V <sub>GS</sub> :<br>(I <sub>D</sub> = 4.0 Adc)<br>(I <sub>D</sub> = 8.0 Adc)<br>(I <sub>D</sub> = 4.0 Adc, T <sub>J</sub> = 100°C) | = 10 V)                                                    | V <sub>DS(on)</sub> | _<br>_<br>_ | 2.0<br>4.5<br>3.2 | Vdc         |

| Static Drain-Source On-Resistance<br>(VGS = 10 Vdc, ID = 4.0 Adc)                                                                                            |                                                            | 「DS(on)             | _           | 0.5               | Ohms        |

| Forward Transconductance<br>(VDS = 15 V, ID = 4.0 A)                                                                                                         |                                                            | 9fs                 | 2.0         | _                 | mhos        |

| SAFE OPERATING AREAS                                                                                                                                         |                                                            |                     |             |                   | <del></del> |

| Forward Biased Safe Operating                                                                                                                                | Area                                                       | FBSOA               |             | See Figure 9      |             |

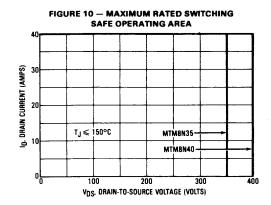

| Switching Safe Operating Area                                                                                                                                |                                                            | SSOA                |             | See Figure 10     |             |

| DYNAMIC CHARACTERISTIC                                                                                                                                       | :s                                                         |                     |             |                   |             |

| Input Capacitance                                                                                                                                            |                                                            | Ciss                | _           | 650               | pF          |

| Output Capacitance                                                                                                                                           | (V <sub>DS</sub> = 25 V, V <sub>GS</sub> = 0, f = 1.0 MHz) | Coss                |             | 300               | pF          |

| Reverse Transfer Capacitance                                                                                                                                 |                                                            | C <sub>rss</sub>    |             | 80                | pF          |

| SWITCHING CHARACTERIST                                                                                                                                       | ICS* (Tj = 100°C)                                          |                     |             |                   |             |

| Turn-On Delay Time                                                                                                                                           |                                                            | t <sub>d(on)</sub>  | _           | 50                | ns          |

| Rise Time                                                                                                                                                    | (V <sub>DS</sub> = 25 V, I <sub>D</sub> = 4.0 A,           | tr                  |             | 150               | ns          |

| Turn-Off Delay Time                                                                                                                                          | R <sub>gen</sub> = 50 ohms)                                | td(off)             | _           | 100               | ns          |

| Fall Time                                                                                                                                                    | [                                                          | tf                  |             | 50                | ns          |

| SOURCE DRAIN DIODE CHA                                                                                                                                       | RACTERISTICS*                                              |                     |             |                   |             |

|                                                                                                                                                              | Ob                                                         |                     | Completed   | Ŧ                 |             |

|                      | Characteristic                       | Symbol | Тур | Unit |

|----------------------|--------------------------------------|--------|-----|------|

| Forward On-Voltage   | IS = 8.0 A                           | VSD    | 1.7 | Vdc  |

| Forward Turn-On Time | V <sub>GS</sub> = 0, di/dt = 25 A/μs | ton    | 80  | ns   |

See Figures 15 and 16

Reverse Recovery Time

#### **RESISTIVE SWITCHING**

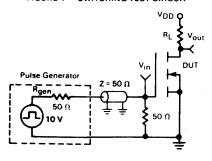

FIGURE 1 - SWITCHING TEST CIRCUIT

FIGURE 2 - SWITCHING WAVEFORMS

700

3

<sup>\*</sup>Pulse Test: Pulse Width ≤300 μs, Duty Cycle ≤2%.

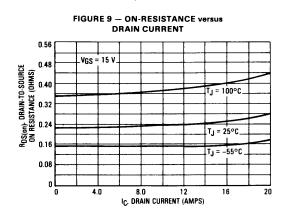

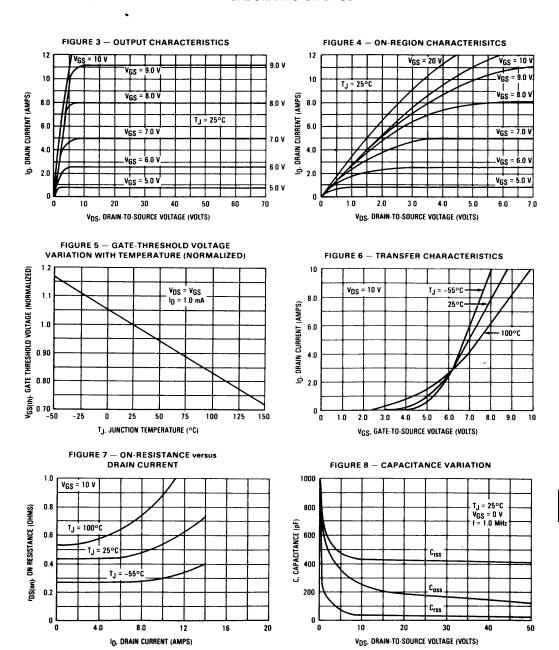

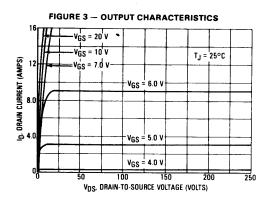

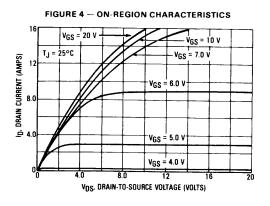

#### TYPICAL CHARACTERISTICS

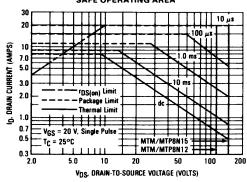

#### SAFE OPERATING AREA INFORMATION

FIGURE 9 — MAXIMUM RATED FORWARD BIASED SAFE OPERATING AREA

# FIGURE 10 — MAXIMUM RATED SWITCHING SAFE OPERATING AREA

#### **FORWARD BIASED**

The data of Figure 9 is based on  $T_C = 25^{\circ}C$ ;  $T_{J(pk)}$  is a variable depending on the power level. The allowable current at the voltages shown in Figure 9 may be calculated for any case temperature with the aid of the following equation:

$$I_D(T_C) = I_D(25^{\circ}C)$$

$$1 - \frac{T_C - 25^{\circ}C}{P_D R_{\theta}JC}$$

where

I<sub>D</sub>(T<sub>C</sub>)

= the maximum allowable current at a case temperature, T<sub>C</sub>.

$I_D(25^{\circ}C)$  = the maximum allowable current at a given voltage from Figure 9.

$P_D$  = the rated power dissipation at  $T_C$  = 25°C.  $R_{\theta JC}$  = the rated steady state thermal resistance For various pulse widths and duty cycles, substitute  $R_{\theta JC(t)}$  determined from Figures 11 and 12 for  $R_{\theta JC}$

#### **SWITCHING SAFE OPERATING AREA**

The switching safe operating area (SOA) of Figure 10, is the boundary that the load line may traverse without incurring damage to the MOSFET. The fundamental limits are the peak current, IpM and the breakdown voltage,  $V_{(BR)DSS}$ . The switching SOA shown in Figure 10 is applicable for both turn-on and turn-off of the devices for switching times less than one microsecond.

100

200 300 500 1000

### THERMAL RESPONSE

2.0 3.0

t, TIME (ms)

10

0.3

10

#### TMOS POWER FET CONSIDERATIONS

Switching Speed — The switching speeds of these devices are dependent on the driving impedance. Extremely fast switching speeds can be attained by driving the gate from a voltage source.

0.01

0.02 0.03

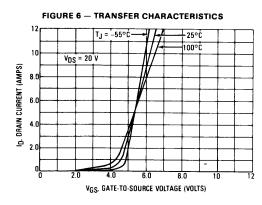

Transfer Characteristics — The transfer characteristics are linear at drain currents of 3.0 Amps. (See Figure 6.) Linear amplifiers with high frequency response can be designed using this product.

**Gate Termination** — The gate of these devices are essentially capacitors. Circuits that leave the gate open-circuited or floating should be avoided. These conditions can result in turn-on of the

devices due to voltage build-up on the input capacitor due to leakage currents or pickup.

Gate Protection — These devices do not have an internal monolithic zener diode from gate to source. The addition of an internal zener diode may result in detrimental effects on the reliability of a power MOSFET. If gate protection is required, an external zener diode is recommended.

Handling and Packaging — MOS ICs are susceptible to damage from electrostatic charge. Experience has shown that these devices are more rugged than MOS ICs. This is primarily due to the comparatively larger capacitances associated with power devices, however, reasonable precautions in handling and packaging MOS devices should be observed.

#### TMOS SOURCE TO DRAIN DIODE CHARACTERISTICS

In the fabrication of a TMOS FET, a diode is formed across the source-to-drain terminals as shown in Figure 15. Reversal of the drain voltage will cause current flow in the reverse direction. This

> FIGURE 13 - TMOS FET WITH SOURCE-TO-DRAIN DIODE

diode may be used in circuits requiring external fast recovery diodes, therefore, typical characteristics of the on voltage, forward turn-on and reverse recovery times are given.

FIGURE 14 - DIODE TURN-ON TEST CIRCUIT

FIGURE 15 - DIODE TURN-ON WAVEFORMS

FIGURE 16 - REVERSE RECOVERY CHARACTERISTIC

FIGURE 17 - JEDEC REVERSE RECOVERY CIRCUIT

R2 = 250 Ohms D1 = 1N4723 D2 = 1N4001 D3 = 1N4933 SCR1 = MCR729-10 C1 = 0.5 to 50 µF C2 = 4000 μF L1 = 1.0 - 27 μH

R1 = 50 Ohms

- T1 = Variac Adjusts I(PK) and di/di T2 = 1:1

- T3 = 1:1 (to trigger circuit)

## Designer's Data Sheet

# N-CHANNEL ENHANCEMENT MODE SILICON GATE TMOS POWER FIELD EFFECT TRANSISTOR

These TMOS Power FETs are designed for high voltage, high speed power switching applications such as line operated switching regulators, and converters.

- Silicon Gate for Fast Switching Speeds Switching Times Specified at 100°C

- Designer's Data IDSS, VDS(on) and SOA Specified at Elevated Temperature

- Rugged SOA is Power Dissipation Limited

- Source to Drain Diode Characterized for Use With Inductive Loads

- Low Drive Requirement, V<sub>G(th)</sub> = 4.5 Volts (max)

#### **MAXIMUM RATINGS**

| Rating                                                            | Symbol                            | MTM8N35    | MTM8N40 | Unit          |

|-------------------------------------------------------------------|-----------------------------------|------------|---------|---------------|

| Drain — Source Voltage                                            | V <sub>DSS</sub>                  | 350        | 400     | Vdc           |

| Drain — Gate Voltage<br>(R <sub>GS</sub> = 1.0 mΩ)                | VDGR                              | 350        | 400     | Vdc           |

| Gate — Source Voltage                                             | ∨ <sub>GS</sub>                   | ±          | 20      | Vdc           |

| Drain Current<br>Continuous<br>Pulsed                             | I <sub>D</sub>                    | 8.0<br>40  |         | Adc           |

| Gate Current — Pulsed                                             | <sup>I</sup> GM                   | 1.5        |         | Adc           |

| Total Power Dissipation @ T <sub>C</sub> = 25°C Derate above 25°C | PD                                | 150<br>1.2 |         | Watts<br>W/°C |

| Operating and Storage<br>Temperature Range                        | T <sub>J</sub> , T <sub>stg</sub> | -65 to 150 |         | °C            |

#### THERMAL CHARACTERISTICS

| Thermal Resistance Junction to Case                                           | R <sub>θ</sub> JC | 0.83 | °C/W |

|-------------------------------------------------------------------------------|-------------------|------|------|

| Maximum Lead Temp. for<br>Soldering Purposes, 1/8"<br>from case for 5 seconds | TL                | 275  | °C   |

#### Designer's Data for "Worst Case" Conditions

The Designer's Data Sheet permits the design of most circuits entirely from the information presented. Limit data — representing device characteristics boundaries — are given to facilitate "worst case" design.

#### **8 AMPERE**

#### N-CHANNEL TMOS POWER FET

r<sub>DS(on)</sub> = 0.55 OHM 350 and 400 VOLTS

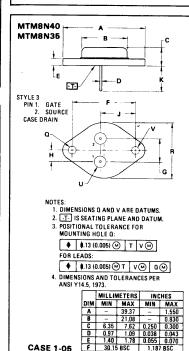

10.92 BSC

5.46 BSC 16.89 BSC

Q

3.81

4.19

0.150

0.165

R

26.67

1,050

U

4.83

5.33

0.190

0.210

V

3.81

4.19

0.150

0.165

TO-3

DS3423R1

| Chara                                                                                                                                          | ecteristic                                                 | Symbol              | Min           | Max               | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------|---------------|-------------------|------|

| OFF CHARACTERISTICS                                                                                                                            |                                                            |                     |               |                   |      |

| Drain-Source Breakdown Voltag<br>(VGS = 0, ID = 5.0 mA)                                                                                        | ge<br>MTM8N35<br>MTM8N40                                   | V(BR)DSS            | 350<br>400    | _                 | Vdc  |

| Zero Gate Voltage Drain Curren<br>(VDS = 0.85 Rated VDSS, VGS<br>TJ = 100°C                                                                    |                                                            | DSS                 | _             | 0.25<br>2.5       | mAdc |

| Gate-Body Leakage Current<br>(VGS = 20 Vdc, VDS = 0)                                                                                           |                                                            | IGSS                | _             | 500               | nAdc |

| ON CHARACTERISTICS*                                                                                                                            |                                                            |                     |               |                   |      |

| Gate Threshold Voltage<br>(I <sub>D</sub> = 1.0 mA, V <sub>DS</sub> = V <sub>GS</sub> )<br>T <sub>J</sub> = 100°C                              |                                                            | VGS(th)             | 2.0<br>1.5    | 4.5<br>4.0        | Vdc  |

| Drain-Source On-Voltage (VGS<br>(I <sub>D</sub> = 4.0 Adc)<br>(I <sub>D</sub> = 8.0 Adc)<br>(I <sub>D</sub> = 4.0 Adc, T <sub>J</sub> = 100°C) | = 10 V)                                                    | V <sub>DS(on)</sub> | -<br>-<br>-   | 3.2<br>8.0<br>5.6 | Vdc  |

| Static Drain-Source On-Resistance<br>(VGS = 10 Vdc, ID = 4.0 Adc)                                                                              |                                                            | <sup>r</sup> DS(on) | _             | 0.55              | Ohms |

| Forward Transconductance<br>(V <sub>DS</sub> = 15 V, I <sub>D</sub> = 4.0 A)                                                                   |                                                            | 9fs                 | 3.0           | _                 | mhos |

| SAFE OPERATING AREAS                                                                                                                           |                                                            |                     |               |                   |      |

| Forward Biased Safe Operating                                                                                                                  | Area                                                       | FBSOA               | See Figure 9  |                   |      |

| Switching Safe Operating Area                                                                                                                  |                                                            | SSOA                | See Figure 10 |                   |      |

| DYNAMIC CHARACTERISTIC                                                                                                                         | cs                                                         |                     |               |                   |      |

| Input Capacitance                                                                                                                              |                                                            | C <sub>iss</sub>    |               | 1800              | pF   |

| Output Capacitance                                                                                                                             | (V <sub>DS</sub> = 25 V, V <sub>GS</sub> = 0, f = 1.0 MHz) | Coss                |               | 350               | pF   |

| Reverse Transfer Capacitance                                                                                                                   |                                                            | C <sub>rss</sub>    |               | 150               | pF   |

| SWITCHING CHARACTERIST                                                                                                                         | rics* (T <sub>J</sub> = 100°C)                             |                     |               |                   |      |

| Turn-On Delay Time                                                                                                                             |                                                            | <sup>t</sup> d(on)  |               | 60                | ns   |

| Rise Time                                                                                                                                      | (V <sub>DS</sub> = 125 V, I <sub>D</sub> = 4.0 A,          | t <sub>r</sub>      |               | 150               | ns   |

| Turn-Off Delay Time                                                                                                                            | R <sub>gen</sub> = 50 ohms)                                | td(off)             |               | 200               | ns   |

| Fall Time                                                                                                                                      | -                                                          | tf                  |               | 120               | ns   |

#### **SOURCE DRAIN DIODE CHARACTERISTICS\***

|                       | Characteristic                       | Symbol          | Тур | Unit |

|-----------------------|--------------------------------------|-----------------|-----|------|

| Forward On-Voltage    | I <sub>S</sub> = 8.0 A               | V <sub>SD</sub> | 1.0 | Vdc  |

| Forward Turn-On Time  | $V_{GS} = 0$ , di/dt = 25 A/ $\mu$ s | ton             | 175 | ns   |

| Reverse Recovery Time | See Figures 14 and 15                | trr             | 600 | ns   |

<sup>\*</sup>Pulse Test: Pulse Width ≤300 μs, Duty Cycle ≤2%.

### **RESISTIVE SWITCHING**

### FIGURE 1 - SWITCHING TEST CIRCUIT

### FIGURE 2 — SWITCHING WAVEFORMS

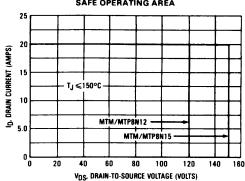

#### SAFE OPERATING AREA INFORMATION

#### **FORWARD BIASED**

The data of Figure 9 is based on  $T_C = 25^{\circ}C$ ;  $T_{J(pk)}$  is a variable depending on the power level. The allowable current at the voltages shown in Figure 9 may be calculated for any case temperature with the aid of the following equation:

$$I_D(T_C) = I_D(25^{\circ}C) \left[ 1 - \frac{T_C - 25^{\circ}C}{P_D R_{\theta J}C} \right]$$

where

$I_D(T_C)$  = the maximum allowable current at a case temperature,  $T_C$ .

$I_D(25^{\circ}C)$  = the maximum allowable current at a given voltage from Figure 9.

from Figure 9.

$P_D$  = the rated power dissipation at  $T_C$  = 25°C.  $R_{\theta JC}$  = the rated steady state thermal resistance For various pulse widths and duty cycles, substitute  $R_{\theta JC(t)}$  determined from Figure 11 for  $R_{\theta JC}.$

#### **SWITCHING SAFE OPERATING AREA**

The switching safe operating area (SOA) of Figure 10, is the boundary that the load line may traverse without incurring damage to the MOSFET. The fundamental limits are the peak current, I<sub>DM</sub> and the breakdown voltage, V<sub>(BR)DSS</sub>. The switching SOA shown in Figure 10 is applicable for both turn-on and turn-off of the devices for switching times less than one microsecond.

#### TYPICAL CHARACTERISTICS

#### FIGURE 11 - THERMAL RESPONSE

#### TMOS SOURCE TO DRAIN DIODE CHARACTERISTICS

In the fabrication of a TMOS FET, a diode is formed across the source-to-drain terminals as shown in Figure 11. Reversal of the drain voltage will cause current flow in the reverse direction. This

FIGURE 12 — TMOS FET WITH SOURCE-TO-DRAIN DIODE

FIGURE 14 — DIODE TURN-ON WAVEFORMS

diode may be used in circuits requiring external fast recovery diodes, therefore, typical characteristics of the on voltage, forward turn-on and reverse recovery times are given.

FIGURE 13 — DIODE TURN-ON TEST CIRCUIT

FIGURE 15 — REVERSE RECOVERY CHARACTERISTIC

FIGURE 16 - JEDEC REVERSE RECOVERY CIRCUIT

R1 = 50 Ohms R2 = 250 Ohms D1 = 1N4723 D2 = 1N4001 D3 = 1N4933 SCR1 = MCR729-10

C1 = 0.5 to 50  $\mu$ F C2 = 4000  $\mu$ F L1 = 1.0–27  $\mu$ H

T1 = Variac Adjusts I<sub>(PK)</sub> and di/dt T2 = 1:1

T3 = 1:1 (to trigger circuit)

#### TMOS POWER FET CONSIDERATIONS

Switching Speed — The switching speeds of these devices are dependent on the driving impedance. Extremely fast switching speeds can be attained by driving the gate from a voltage source.

**Transfer Characteristics** — The transfer characteristics are linear at drain currents of 2.0 Amps. (See Figure 6.) Linear amplifiers with high frequency response can be designed using this product.

**Gate Voltage Rating** — Never exceed the gate voltage rating of  $\pm 20$  V. Exceeding the rated VGS can result in permanent damage to the oxide layer in the gate region.

Gate Termination — The gate of these devices are essentially capacitors. Circuits that leave the gate open-circuited or floating should be avoided. These conditions can result in turn-on of the

devices due to voltage build-up on the input capacitor due to leakage currents or pickup.

Gate Protection — These devices do not have an internal monolithic zener diode from gate to source. The addition of an internal zener diode may result in detrimental effects on the reliability of a power MOSFET. If gate protection is required, an external zener diode is recommended.

Handling and Packaging — MOS ICs are susceptible to damage from electrostatic charge. Experience has shown that these devices are more rugged than MOS ICs. This is primarily due to the comparatively larger capacitances associated with power devices, however, reasonable precautions in handling and packaging MOS devices should be observed.