## **BA1320**

The BA1320 is a monolithic integrated circuit consisting of a phase-locked loop FM stereo demodulator. It was designed for use in battery-operated stereo cassette recorders as well as car stereo equipment, and operates on a low-voltage, internally-stabilized supply. Stable operation is possible as low as  $V_{CC} = 5.4V$ .

A pin is provided for stopping the VCO, thus facilitating this function for AM reception.

A separation control pin does not require input compensation and enables stable high separation.

This PLL device requires few externallyconnected components and is designed for ease of adjustment.

### **Features**

- A PLL is used for high multiplexing performance.

- 2. Stable operation at low voltages  $(V_{CC} = 5.4V \text{ min})$

- 3. Low lamp lighting level (typically 6.5mV)

- 4. Provided with a separation control pin (pin 8)

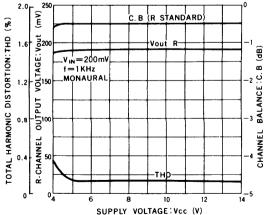

- 5. Ä pin is provided for stopping the VCO and for monaural muting. (pin 9)

- 6. Output voltage is available with low loss ( $G_V = -1 dB$  typically).

- 7. Low distortion (typically 0.3%)

- 8. Good SCA rejection ratio (typically 80dB)

- Designed for compatibility with 14-pin-70 type devices

# **Applications**

- 1. Stereo radio cassettes

- 2. Car stereos

- 3. Home stereos

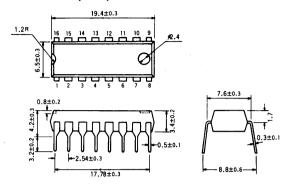

## Dimensions (mm)

Fig. 1

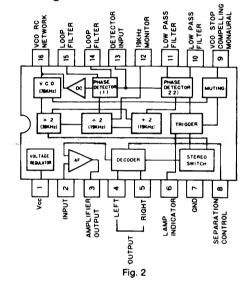

**Block Diagram**

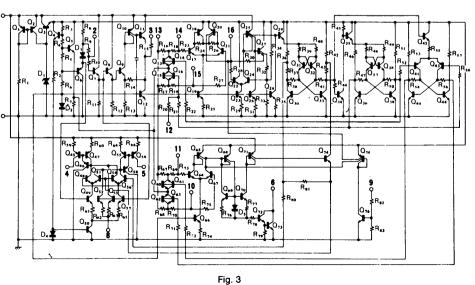

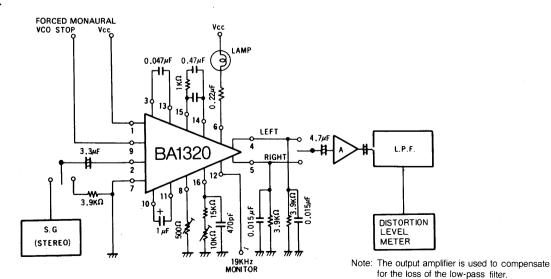

#### Circuit Diagram

## Absolute Maximum Ratings ( $T_a = 25^{\circ}C$ )

| Parameter             | Symbol           | Limits          | Unit |  |

|-----------------------|------------------|-----------------|------|--|

| Supply voltage        | V <sub>CC</sub>  | 14              | V    |  |

| Power dissipation     | P <sub>d</sub>   | 550*            | mW   |  |

| Operating temperature | T <sub>opr</sub> | <b>−25</b> ~+75 | °C   |  |

| Storage temperature   | T <sub>stg</sub> | −55~+125        | °C   |  |

| Lamp drive current    | ILAMP            | 75              | mA   |  |

<sup>\*</sup>Derating is done at  $5.5 \text{mW}/^{\circ}\text{C}$  for operation above  $T_a = 25 ^{\circ}\text{C}$ .

#### **Electrical Characteristics**

(T\_a = 25°C,  $V_{CC}$  = 12V,  $V_{IN}$  = 350mV (L+R = 90%, Pilot = 10%), f = 1kHz)

| Parameter                         | Symbol             | Min      | Тур | Max                                             | Unit | Conditions                         | Test circuit |

|-----------------------------------|--------------------|----------|-----|-------------------------------------------------|------|------------------------------------|--------------|

| Maximum composite<br>input signal | VINI               | 350      | _   | _                                               | mV   | THD = 1%, L + R = 90%,<br>P = 10%  | Fig. 16      |

| Maximum monaural<br>input signal  | V <sub>IN2</sub>   | 350      | _   | -                                               | mV   | THD = 1%                           | Fig. 16      |

| Input impedance                   | Zin                | <b> </b> | 30  |                                                 | kΩ   |                                    | Fig. 16      |

| Channel separation                | Sep                | 35       | 40  | <del>-                                   </del> | dB   |                                    | Fig. 16      |

| Audio output voltage              | V <sub>OUT</sub>   | _        | 310 | -                                               | mV   | V <sub>IN</sub> = 350mV            | Fig. 16      |

| Channel balance                   | СВ                 | _        | _   | 2                                               | dB   |                                    | Fig. 16      |

| Total harmonic distortion         | THD                | _        | 0.3 | _                                               | %    |                                    | Fig. 16      |

| Lamp on level                     | Lon                |          | 6.5 | <b> </b>                                        | mV   | Pilot                              | Fig. 16      |

| Lamp hysteresis                   | Hys                | _        | 3   | _                                               | dB   |                                    | Fig. 16      |

| Capture range                     | CR                 |          | ±5  | _                                               | %    |                                    | Fig. 16      |

| Carrier leakage                   | CL                 | _        | 35  | _                                               | dB   | f = 19kHz                          | _            |

| Carrier leakage                   | CL                 |          | 45  | -                                               | dB   | f = 38kHz                          | _            |

| SCA Rejection ratio               | SCA <sub>rej</sub> | -        | 80  | _                                               | dB   | L + R = 80%, P = 10%,<br>SCA = 10% | _            |

| Muting threshold voltage          | U <sub>TH</sub>    | _        | 1   | _                                               | ٧    |                                    | Fig. 16      |

| Operating voltage range           | Vcc                | 5.4      | _   | 14                                              | ٧    |                                    | Fig. 16      |

| Quiescent supply current          | lcc                | _        | 15  | -                                               | mA   |                                    | Fig. 16      |

## **Electrical Characteristic Curves**

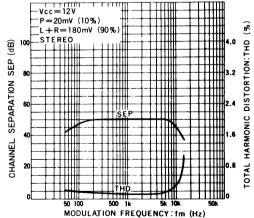

Fig. 4 Total harmonic distortion and channel separation vs. modulation frequency

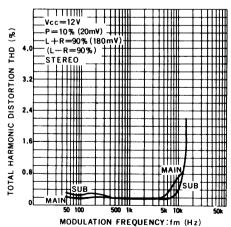

Fig. 5 Main and sub-signal distortion vs. modulation frequency

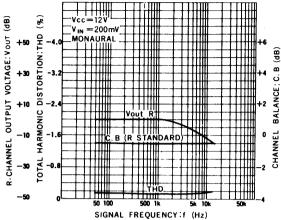

Fig. 6 Channel balance, R-channel output voltage and total harmonic distortion vs. frequency

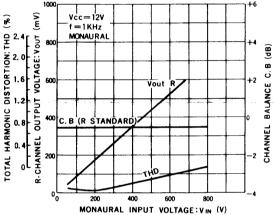

Fig. 8 Channel balance, total harmonic distortion, and R-channel output voltage vs. input voltage

Fig. 10 Channel balance, total harmonic distortion, and R-channel output voltage vs. supply voltage

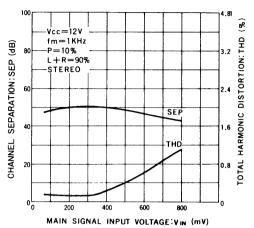

Fig. 7 Total harmonic distortion and channel separation vs. main signal input voltage

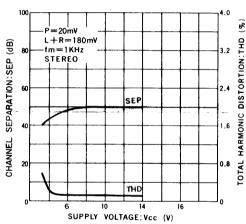

Fig. 9 Total harmonic distortion and channel separation vs. supply voltage

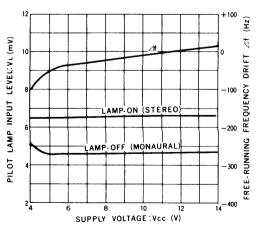

Fig. 11 Free-running frequency drift and pilot lamp input level vs. supply voltage

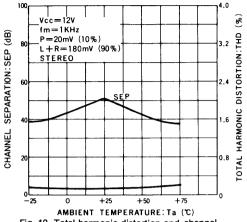

Fig. 12 Total harmonic distortion and channel separation vs. ambient temperature

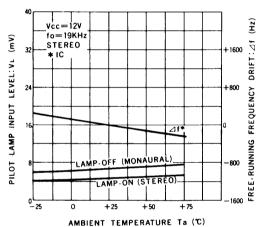

Fig. 14 Free-running frequency drift and pilot lamp input level vs. ambient temperature

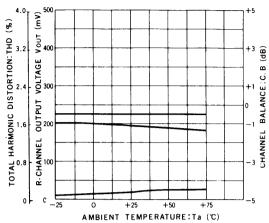

Fig. 13 Channel balance, R-channel output voltage and total harmonic distortion vs. ambient temperature

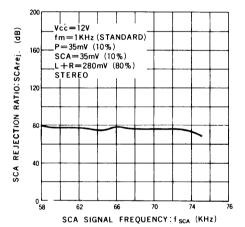

Fig. 15 SCA Rejection ratio vs. SCA signal frequency

#### **Test Circuit**

Fig. 16

#### Circuit Description (See Fig. 3) 5. Muting

1. Input Amplifier

The input amplifier amplifies the composite signal input at pin 2 and outputs this signal at pin 3. This signal becomes the input for the phase detector (pin 13). The amplifier gain is approximately 7dB. Subsequently, the decoder outputs a signal through an emitterfollower.

2. PLL

The PLL is composed of phase detector 1, DC amplifier, VCO, and divider (38kHz, 19kHz), It acts to tune the composite signal input at pin 13 to the pilot signal.

3. Pilot Signal Detector

The phase detector 2 outputs a DC voltage to the trigger stage according to the pilot signal level. When this reaches above a specified level, the trigger stage operates, turning the stereo switch on, and the 38kHz switching signal is input to the decoder. With the PLL in the locked condition, the phase of the 19kHz signal is 90° skewed from the input pilot signal, and dividers are used to achieve synchronization, outputting an in-phase signal to the detector 2.

Decoder

In the monaural mode, the right-and left-channel input signals are output as is. When the stereo switch operates, the input composite signal is divided between the right and left channels and output in two parts. For this type of operation, separation may be controlled by connecting a variable resistor to pin 8.

By applying a DC voltage to pin 9, the VCO may be stopped, forcing the monaural mode.

6. Power Supply Muting

This circuit senses the power supply voltage and controls VCO oscillations. When the power supply is turned on. the VCO is in the run condition when V<sub>CC</sub> is typically 3.6V or higher, and in the stop condition when the supply voltage is typically 3.2V or lower.

7. Voltage Regulator

This internal voltage regulator is used to provide a stable supply voltage for the various circuits of the BA1320.

## **Externally Connected** Components (See Fig. 16)

- 1. Input Coupling Capacitor (Pin 2) This capacitor is used to couple the BA1320 to the detector stage. The recommended value is 2.2~3.2 µF. If smaller values of capacitance are used. low-frequency separation will worsen, and if larger values are used. the DC operating point (pin 2) will require time for stabilization.

- 2. Output Resistor and Capacitor (Pins 4 and 5)

These components provide right-and left-channel output load circuits. The recommended value are  $3.9k\Omega$  and  $0.015\mu$ F. Voltage gain increases as the resistance is increased. This RC circuit comprises the deemphasis circuit.

Separation Control (Pin 8)

This component is a variable resistor used to adjust the output-signal separation. The test circuit shown uses a  $500\Omega$  potentiometer. However, actual circuits should ideally use a  $1k\Omega$  potentiometer. It is also possible to use a fixed resistor for this component.

- Low-Pass Filter (Pins 10 and 11) This capacitor is used to filter the pilot signal detected by the phase detector 2. The recommended capacitance is  $1\sim2.2\mu\text{F}$ . If the capacitance is smaller, the lamp may light improperly when a large monaural input signal or noise is received. If, however, the capacitance is larger, it will take more time to switch between monaural and stereo modes.

- Preamplifier Output Capacitor (Pins 3 and 13)

This capacitor is used to couple the preamplifier output and the phase detector input. The recommended capacitance is 0.047 µF. The capacitance is intentionally rather low beause it is theoretically sufficient to pass only the 19kHz signal.

Loop Filter (Pins 14 and 15) This is the low-pass filter for the PLL. The recommended values are  $0.22 \mu F$ .  $0.47\mu$ F, and 1k $\Omega$ . This filter determines

the capture range. When changing these values, study the operating conditions carefully.

VCO RC Network (Pin 16) Since the VCO has a negative temperature coefficient, the RC network must compensate by using a polystyrene capacitor and a resistor. The recommended values are 470pF for the capacitance and  $15k\Omega$  and  $10k\Omega$  for the fixed and variable resistors, respectively.

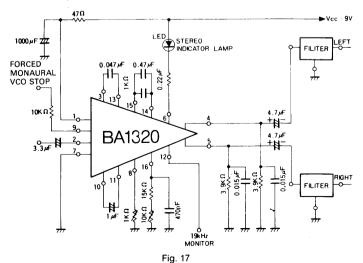

### Application Example

The output voltage is attenuated by the output filters (19kHz, 38kHz). This is done also by the  $1k\Omega$  variable resistor controlling separation at pin 8. If pin 9 is connected through a switch and  $10k\Omega$  to  $V_{CC}$ , it may be used for auto/monaural switching. Also, if connected to the AM IF stage V<sub>CC</sub>. FM→AM switching can be used to control the inhibition of VCO oscillations.