## Precision Monolithics Inc.

# **FEATURES**

| High Slew Rate                                 | 130V/μs Min |

|------------------------------------------------|-------------|

| • Fast Settling Time (+10V, 0.1%)              |             |

| • Gain-Bandwidth Product (A <sub>VCL</sub> = + | 5) 80MHz Ty |

| Low Supply Current                             | 8mA Max     |

| Low Noise                                      | 8nV/√Hz Typ |

| Low Offset Voltage                             | 1mV Max     |

- High Output Current .....±80mA Typ **Eliminates External Buffer**

- Standard 8-Pin Packages

- Available in Die Form

# ORDERING INFORMATION 1

|                                                       |                | PAC                      | CKAGE                |                               |                                   |

|-------------------------------------------------------|----------------|--------------------------|----------------------|-------------------------------|-----------------------------------|

| T <sub>A</sub> = +25°C<br>V <sub>OS</sub> MAX<br>(mV) | TO-99<br>8-PIN | HERMETIC<br>DIP<br>8-PIN | PLASTIC<br>8-PIN     | HERMETIC<br>LCC<br>20-CONTACT | OPERATING<br>TEMPERATURE<br>RANGE |

| 1.0                                                   | OP64AJ*        | OP64AZ*                  | _                    | OP64ARC/883                   | MIL                               |

| 1.0                                                   | OP64EJ         | OP64EZ                   | -                    | -                             | XIND                              |

| 2.0                                                   | OP64FJ         | OP64FZ                   | _                    | _                             | XIND                              |

| 2.5                                                   | -              | - , : ,                  | OP64GP               |                               | XIND.                             |

| 2.5                                                   |                |                          | OP64GS <sup>††</sup> |                               | XIND                              |

XIND = Extended Industrial Temperature Range, -40°C to +85°C

- For devices processed in total compliance to MIL-STD-883, add /883 after part number. Consult factory for 883 data sheet.

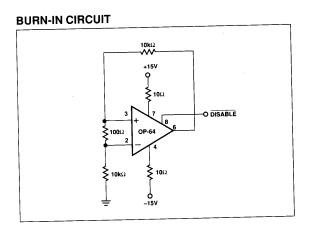

- Burn-in is available on commercial and industrial temperature range parts in CerDIP, plastic DIP, and TO-can packages. For ordering information, see PMI's Data Book, Section 2.

- †† For availability and burn-in information on SO and PLCC packages, contact your local sales office.

# GENERAL DESCRIPTION

The OP-64 is a high-performance monolithic operational amplifier that combines high speed and wide bandwidth with low power consumption. Advanced processing techniques have Continued

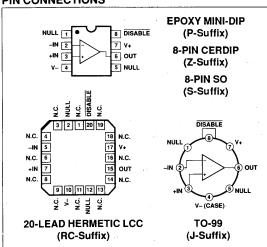

# **PIN CONNECTIONS**

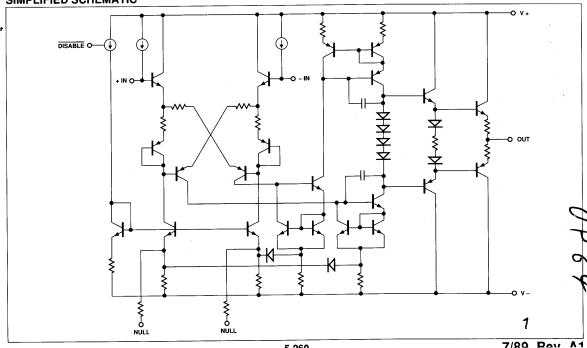

# SIMPLIFIED SCHEMATIC

### **GENERAL DESCRIPTION** Continued

enabled PMI to make the OP-64 superior in cost and perform ance to many dielectrically-isolated and hybrid op amps.

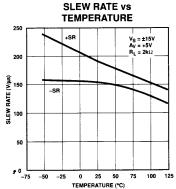

Slew rate of the OP-64 is over 130V/us. It is stable in gains of ≥5 and has a settling time of only 100ns to 0.1% with a 10V step input. However, unlike other high-speed op amps which have high supply requirements, the OP-64 needs less than 8mA of supply current. This enables the OP-64 to be packaged in space saving 8-pin packages. The OP-64 can deliver ±80mA of output current eliminating the need for a separate buffer amplifier in many applications. Noise of the OP-64 is only 8nV√Hz, reducing system noise in wideband applications. In addition to its dynamic performance, the OP-64 adds DC precision with an input offset voltage of under 1mV.

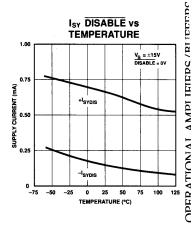

The OP-64 is an ideal choice for RF, video and pulse amplifier applications and in new designs can replace the HA-5190/95 or EL-2190/95 with improved performance and reduced power consumption. Its high output current also suits the OP-64 for use in A/D or cable driver applications. The OP-64 includes a DIS-ABLE pin which, when set low, shuts the amplifier off and reduces the supply current to 0.75mA.

| <b>ABSOLUTE MAXIMUN</b> | I RATINGS (Note 1) |

|-------------------------|--------------------|

|-------------------------|--------------------|

| Supply Voltage             | , , |

|----------------------------|-----|

| Input Voltage              |     |

| Differential Input Voltage |     |

| DISABLE Input Voltage Output Short-Circuit Dura Storage Temperature Rai |                          | Supp            | ly Voltage  |

|-------------------------------------------------------------------------|--------------------------|-----------------|-------------|

| (J, Z, RC)                                                              | •                        | 65°C            | to +175°C   |

| (P, S)                                                                  |                          |                 |             |

| Operating Temperature F                                                 |                          |                 |             |

| OP-64A (J, Z, RC)                                                       |                          | 55°C            | to +125°C   |

| OP-64E, F (J, Z)                                                        |                          |                 |             |

| OP-64G (P, S)                                                           |                          | –40°(           | C to .+85°C |

| Maximum Junction Temp                                                   |                          |                 |             |

| OP-64A (J ,Z, RC)                                                       |                          | ,               | +175°C      |

| OP-64E, F (J, Z)                                                        |                          |                 | +175°C      |

| OP-64G (P, S)                                                           |                          |                 | +150°C      |

| Lead Temperature (Solde                                                 | ering, 60 sec)           |                 | +300°C      |

| PACKAGE TYPE                                                            | Θ <sub>JA</sub> (Note 2) | Θ <sub>jC</sub> | UNITS       |

| TO-99 (J)                                                               | - 150                    | 18              | °C/W        |

| 8-Pin Hermetic DIP (Z)                                                  | 148                      | 16              | °C/W        |

| 8-Pin Plastic DIP (P)                                                   | 103                      | 43 .            | °C/W        |

| 20-Contact LCC (RC, TC)                                                 | 98                       | 38              | °C/W        |

| 8-Pin SO (S)                                                            | 158                      | 43              | °C/W        |

#### NOTES:

- 1. Absolute maximum ratings apply to both DICE and packaged parts, unless otherwise noted.

- 2.  $\Theta_{iA}$  is specified for worst case mounting conditions, i.e.,  $\Theta_{iA}$  is specified for device in socket for TO, CerDIP, P-DIP, and LCC packages;  $\Theta_{i,k}$  is specified for device soldered to printed circuit board for SO package.

# **ELECTRICAL CHARACTERISTICS** at $V_s = \pm 15V$ , $T_A = +25$ °C, unless otherwise noted.

|                                 |                  |                                                                 |            | OP-64A/I       | =        |            | OP-64F         |               |            | OP-64G         |          |       |

|---------------------------------|------------------|-----------------------------------------------------------------|------------|----------------|----------|------------|----------------|---------------|------------|----------------|----------|-------|

| PARAMETER                       | SYMBOL           | CONDITIONS                                                      | MIN        | TYP            | MAX      | MIN        | TYP            | MAX           | MIN        | TYP            | MAX      | UNITS |

| Offset<br>Voltage               | v <sub>os</sub>  |                                                                 |            | 0.4            | . 1      | -          | 0.8            | 2             |            | 1.2            | 2.5      | mV    |

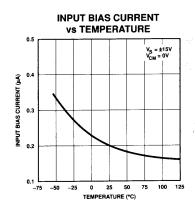

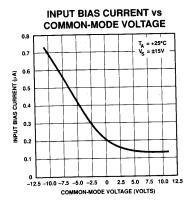

| Input Bias<br>Current           | I <sub>B</sub>   | V <sub>CM</sub> = 0V                                            |            | 0.2            | 1        | _          | 0.4            | 2             | _          | 0.8            | 2.5      | μА    |

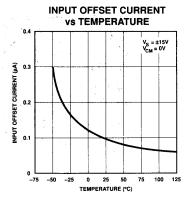

| Input Offset<br>Current         | l <sub>os</sub>  | V <sub>CM</sub> = 0V                                            | -          | 0.1            | 1,       | _          | 0.3            | 2             | ·          | 0.6            | 2.5      | μА    |

| Input Voltage<br>Range          | IVR              | (Note 1)                                                        | ±11        | _              | _        | .±11       | _              | _             | ±11        | -              | -        | ٧     |

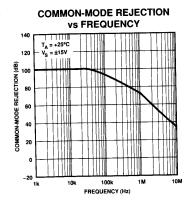

| Common-Mode<br>Rejection        | CMR              | V <sub>CM</sub> = ±11V                                          | 90         | 100            |          | 84         | 94             | _             | 84         | 94             |          | dB    |

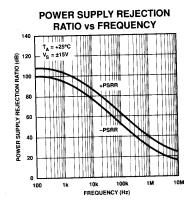

| Power-Supply<br>Rejection Ratio | PSRR             | V <sub>S</sub> = ±5V to ±18V                                    | _          | 5              | 17.8     | _          | 15             | 31.6          | -          | 15             | 31.6     | μV/V  |

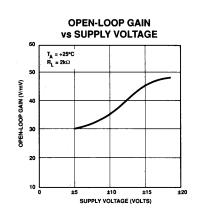

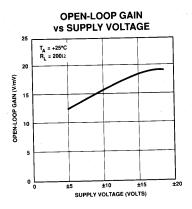

| Large-Signal<br>Voltage Gain    | A <sub>VO</sub>  | $R_L = 2k\Omega, V_O = \pm 10V$ $R_L = 200\Omega, V_O = \pm 5V$ | 30<br>12.5 | 45<br>18       | <i>'</i> | 20<br>10   | 35<br>16       | <u>-</u><br>- | 20<br>10   | 35<br>16       | <u>-</u> | V/mV  |

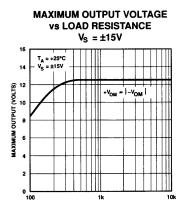

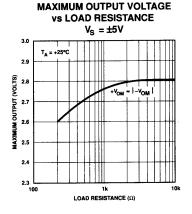

| Output Voltage<br>Swing         | v <sub>o</sub>   | $R_{L} = 2k\Omega$ $R_{L} = 200\Omega$                          | ±11<br>±10 | ±12.5<br>±11.7 |          | ±11<br>±10 | ±12.5<br>±11.7 | -             | ±11<br>±10 | ±12.5<br>±11.7 | -        | ٧     |

| Output<br>Current               | l <sub>out</sub> |                                                                 | -          | ±80            | -        | _          | ±80            | _             | _          | ±80            |          | mA    |

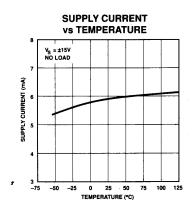

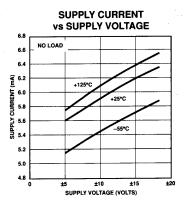

| Supply<br>Current               | I <sub>SY</sub>  | No Load                                                         | -          | 6.2            | 8        | _          | 6.2            | 8             | _          | 6.2            | 8        | mA    |

# NOTE:

<sup>1.</sup> Guaranteed by CMR test.

**ELECTRICAL CHARACTERISTICS** at  $V_S = \pm 15V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.

|                                        |                       |                                      |     | OP-64A/E |              |     | OP-64F |        | OP-64G |      |     |         |

|----------------------------------------|-----------------------|--------------------------------------|-----|----------|--------------|-----|--------|--------|--------|------|-----|---------|

| PARAMETER                              | SYMBOL                | CONDITIONS                           | MIN | TYP      | MAX          | MIN | TYP    | MAX    | MIN    | TYP  | MAX | UNITS   |

| Disable Supply<br>Current              | I <sub>SY DIS</sub>   | DISABLE = 0V Total for both supplies | _   | 0.75     | 1            | _   | 0.75   | 1      | -      | 0.75 | 1   | mA      |

| DISABLE<br>Current                     | I <sub>DIS</sub>      | DISABLE = 0V                         | -   | 0.5      | _            | -   | 0.5    | _      | -      | 0.5  | -   | mA      |

| Slew Rate                              | SR                    | $R_L = 2k\Omega$                     | 130 | 170      | _            | 130 | 170    | _      | 130    | 170  | -   | V/µs    |

| Full-Power<br>Bandwidth                | BW <sub>p</sub>       | (Note 2)                             | 2   | 2.7      | -            | 2   | 2.7    | -      | 2      | 2.7  | -   | MHz     |

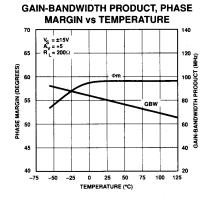

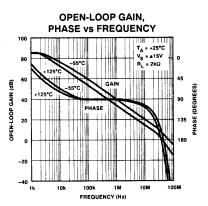

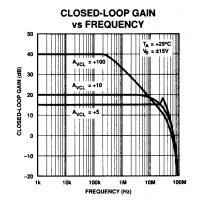

| Gain-Bandwidth<br>Product              | GBWP                  | A <sub>V</sub> = +5                  | -   | 80       | -            | -   | 80     | -      | _      | 80   | -   | MHz     |

| Settling Time                          | t <sub>s</sub>        | 10V Step 0.1%                        | _   | 100      | -            | -   | 100    | -      |        | 100  | -   | ns      |

| Phase Margin                           | ø <sub>m</sub>        | A <sub>V</sub> = +5                  | _   | 57       | _            | _   | 57     | -      | -      | 57   | _   | degrees |

| Input<br>Capacitance                   | C <sub>IN</sub>       |                                      | _   | 5        | -            | _   | 5      |        | · -    | 5    | _   | pF      |

| Open-Loop<br>Output<br>Resistance      | R <sub>O</sub>        |                                      | -   | 30       | <del>-</del> | _   | 30     | _      | · _    | 30   |     | Ω       |

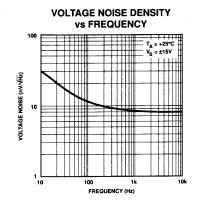

| Voltage                                |                       | f <sub>o</sub> = 10Hz                | -   | 30       | _            | _   | 30     | -      | _      | 30   | _   |         |

| Noise                                  | en                    | f <sub>0</sub> = 100Hz               | -   | 10       | -            | -   | 10     | -      | -      | 10   | -   | nV/√Hz  |

| Density                                | - n                   | $f_o = 1kHz$<br>$f_o = 10kHz$        | _   | 8<br>8   | -            | -   | 8<br>8 | -      | _      | 8    | _   |         |

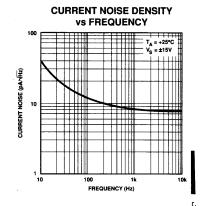

| Current Noise<br>Density               | i <sub>n</sub>        | f <sub>o</sub> = 10kHz               | -   | 7.5      | _            | -   | 7.5    |        |        | 7.5  |     | pA/√Hz  |

| External V <sub>OS</sub><br>Trim Range | $R_{pot} = 20k\Omega$ |                                      | -   | 4        | <del>-</del> | _   | 4      | -<br>- | _      | 4    | -   | mV      |

| Supply Voltage<br>Range                | v <sub>s</sub>        |                                      | ±5  | ±15      | ±18          | ±5  | ±15    | ±18    | ±5     | ±15  | ±18 | V       |

### NOTES:

<sup>1.</sup> Guaranteed by CMR test.

<sup>2.</sup> Guaranteed by slew-rate test and formula  $BW_p = SR/(2\pi 10V_{PEAK})$ .

|                                 |                  | 10                                   | $\pm 15V$ , $-40^{\circ}C \le T_{A} \le +85^{\circ}C$ for OP-64E |       |      |              | OP-64F |     |     | OP-64G |     |            |

|---------------------------------|------------------|--------------------------------------|------------------------------------------------------------------|-------|------|--------------|--------|-----|-----|--------|-----|------------|

| PARAMETER                       | SYMBOL           | CONDITIONS                           | MIN                                                              | TYP   | MAX  | MIN          | TYP    | MAX | MIN | TYP    | MAX | UNITS      |

| Offset<br>Voltage               | v <sub>os</sub>  |                                      | _                                                                | 0.5   | 1.5  | <del>-</del> | 1.0    | 3   |     | 1.5    | 3.5 | mV         |

| Input Bias<br>Current           | I <sub>B</sub>   | V <sub>CM</sub> = 0V                 | _                                                                | 0.3   | 2.5  | _            | 0.5    | 3   | -   | 1.5    | 3.5 | μА         |

| Input Offset<br>Current         | los              | V <sub>C M</sub> = 0V                |                                                                  | 0.2   | 2.5  | -            | 0.5    | 3   | -   | 1.0    | 3.5 | μА         |

| Input Voltage<br>Range          | IVR              | (Note 1)                             | ±11                                                              | _     |      | ±11          | -      | _   | ±11 |        | _   | V          |

| Common-Mode<br>Rejection        | CMR              | V <sub>CM</sub> = ±11                | 86                                                               | 100   |      | 80           | 94     | _   | 80  | 94     |     | dB         |

| Power-Supply<br>Rejection Ratio | PSRR             | $V_{S} = \pm 5V \text{ to } \pm 18V$ | -                                                                | 5     | 31.6 |              | 15     | 50  | _   | 15     | 50  | μV/V       |

|                                 |                  | $R_1 = 2k\Omega$ , $V_0 = \pm 10V$   | 20                                                               | 40    | _    | 15           | 35     | -   | 15  | 35     | -   | V/mV       |

| Large-Signal<br>Voltage Gain    | $A_{VO}$         | $R_1 = 200\Omega, V_0 = \pm 5V$      | 7.5                                                              | 12    | -    | 5            | 10     |     | 5   | 10     |     |            |

|                                 |                  | $R_1 = 2k\Omega$                     | ±11                                                              | ±12.3 |      | ±11          | ±12.3  | -   | ±11 | ±12.3  | _   | · V        |

| Output Voltage<br>Swing         | - v <sub>o</sub> | $R_L = 200\Omega$                    | ±10                                                              | ±11.5 |      | ±10          | ±11.5  |     | ±10 | ±11.5  |     |            |

| Supply<br>Current               | Isy              | No Load                              | -                                                                | 6.3   | 8.5  |              | 6.3    | 8.5 |     | 6.3    | 8.5 | m <i>A</i> |

# NOTE:

**ELECTRICAL CHARACTERISTICS** at  $V_S = \pm 15V$ ,  $-55^{\circ}C \le T_A \le +125^{\circ}C$  for OP-64A, unless otherwise noted.

| PARAMETER                       | SYMBOL          | CONDITIONS                                                              | MIN         | OP-64A<br>TYP | MAX  | UNITS |

|---------------------------------|-----------------|-------------------------------------------------------------------------|-------------|---------------|------|-------|

| Offset<br>Voltage               | v <sub>os</sub> |                                                                         |             | 0.4           | 2    | mV    |

| Input Bias<br>Current           | I <sub>B</sub>  | V <sub>CM</sub> = 0V                                                    |             | 0.35          | 2    | μА    |

| Input Offset<br>Current         | los             | V <sub>C M</sub> = 0V                                                   | _           | 0.3           | 2    | μΑ    |

| Input Voltage<br>Range          | IVR             | (Note 1)                                                                | ±11         |               | _    | V     |

| Common-Mode<br>Rejection        | CMR             | V <sub>CM</sub> = ±11                                                   | 86          | 100           | _    | dB    |

| Power-Supply<br>Rejection Ratio | PSRR            | $V_S = \pm 5V$ to $\pm 18V$                                             | _           | 8             | 31.6 | μV/V  |

| Large-Signal<br>Voltage Gain    | A <sub>VO</sub> | $R_{L} = 2k\Omega, V_{O} = \pm 10V$ $R_{L} = 200\Omega, V_{O} = \pm 5V$ | 20<br>7.5   | 30<br>10      |      | V/mV  |

| Output Voltage<br>Swing         | v <sub>o</sub>  | $R_L = 2k\Omega$<br>$R_L = 200\Omega$                                   | ±11<br>±7.5 | ±12<br>±10    | _    | V     |

| Supply<br>Current               | I <sub>SY</sub> | No Load                                                                 | _           | 6.4           | 8.5  | mA    |

NOTE: 1. Guaranteed by CMR test.

<sup>1.</sup> Guaranteed by CMR test.

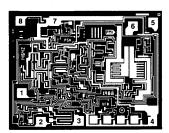

### **DICE CHARACTERISTICS**

DIE SIZE 0.086 x 0.065 inch, 5,590 sq. mils (2.18 x 1.65 mm, 3.60 sq. mm)

- 1. NULL

- 2. -IN

- 3. +IN

- 4. V-

- 5. NULL

- 6. OUT

- 7. V+

- 8. DISABLE

For additional DICE ordering information, refer to PMI's Data Book, Section 2.

# **WAFER TEST LIMITS** at $V_S = \pm 15V$ , $T_A = +25^{\circ}C$ , unless otherwise noted.

| 0.0.445750                      |                  | COMPLETIONS                                                             | OP-64GBC<br>LIMITS | LIAUTO   |

|---------------------------------|------------------|-------------------------------------------------------------------------|--------------------|----------|

| PARAMETER                       | SYMBOL           | CONDITIONS                                                              | LIMITS             | UNITS    |

| Offset Voltage                  | v <sub>os</sub>  | ·                                                                       | 2.5                | mV MAX   |

| Input Bias Current              | I <sub>B</sub>   | V <sub>CM</sub> = 0V                                                    | 2.5                | μΑ ΜΑΧ   |

| Input Offset Current            | Ios              | V <sub>CM</sub> = 0V                                                    | 2.5                | μΑ ΜΑΧ   |

| Input Voltage Range             | IVR              | (Note 1)                                                                | ±11                | V MIN    |

| Common-Mode Rejection           | CMR              | V <sub>CM</sub> = ±11V                                                  | 84                 | dB MIN   |

| Power Supply<br>Rejection Ratio | PSRR             | V <sub>S</sub> = ±5V to ±18V                                            | 31.6               | μV/V MAX |

| Large-Signal<br>Voltage Gain    | A <sub>VO</sub>  | $R_{L} = 2k\Omega, V_{O} = \pm 10V$ $R_{L} = 200\Omega, V_{O} = \pm 5V$ | 20<br>10           | V/mV MIN |

| Output Voltage<br>Swing         | v <sub>o</sub>   | $R_{L} = 2k\Omega$ $R_{L} = 200\Omega$                                  | ±11<br>±10         | V MIN    |

| Slew Rate SR                    | $R_L = 2k\Omega$ |                                                                         | 120                | V/μs MIN |

| Supply Current                  | I <sub>SY</sub>  | No Load                                                                 | 8                  | mA MAX   |

### NOTES:

1. Guaranteed by CMR test.

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard product dice. Consult factory to negotiate specifications based on dice lot qualifications through sample lot assembly and testing.

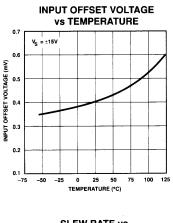

### TYPICAL PERFORMANCE CHARACTERISTICS

### TYPICAL PERFORMANCE CHARACTERISTICS Continued

LOAD RESISTANCE (Ω)

# TYPICAL PERFORMANCE CHARACTERISTICS Continued

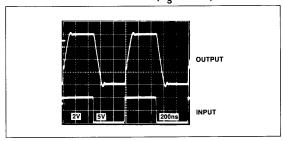

# LARGE SIGNAL RESPONSE $(V_S = \pm 15V)$

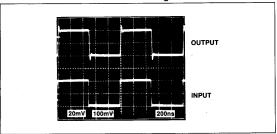

# SMALL SIGNAL RESPONSE $(V_s = \pm 15V)$

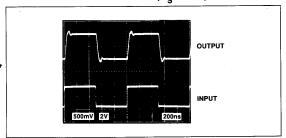

# LARGE SIGNAL RESPONSE ( $V_S = \pm 5V$ )

### APPLICATIONS INFORMATION

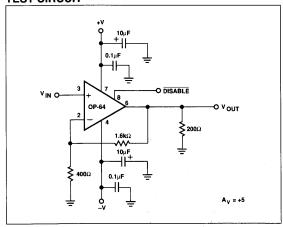

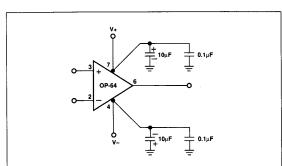

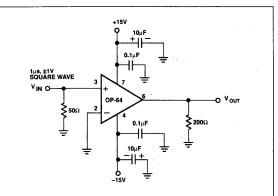

# POWER SUPPLY BYPASSING AND LAYOUT CONSIDERATIONS

Proper power supply bypassing is critical in all high-frequency circuit applications. For stable operation of the OP-64, the power supplies must maintain a low impedance-to-ground over an extremely wide bandwidth. This is most critical when driving a low resistance or large capacitance, since the current required to drive the load comes from the power supplies. A  $10\mu F$  and  $0.1\mu F$  ceramic bypass capacitor are recommended for each supply, as shown in Figure 1, and will provide adequate high-frequency bypassing in most applications. The bypass capacitors should be placed at the supply pins of the OP-64. As with all high frequency amplifiers, circuit layout is a critical factor in

# LARGE AND SMALL SIGNAL RESPONSE TEST CIRCUIT

obtaining optimum performance from the OP-64. Proper high frequency layout reduces unwanted signal coupling in the circuit. When breadboarding a high frequency circuit, use direct point-to-point wiring, keeping all lead lengths as short as possible. Do not use wire-wrap boards or "plug-in" prototyping boards.

During PC board layout, keep all lead lengths and traces as short as possible to minimize inductance. The feedback and gain-setting resistors should be as close as possible to the inverting input to reduce stray capacitance at that point. To further

FIGURE 1: Proper power supply bypassing is required to obtain optimum performance with the OP-64.

reduce stray capacitance, remove the ground plane from the area around the inputs of the OP-64. Elsewhere, the use of a solid unbroken ground plane will insure a good high-frequency ground.

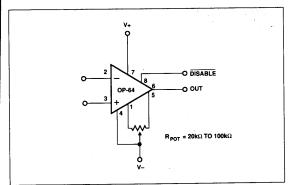

FIGURE 2: Input Offset Voltage Nulling

### OFFSET VOLTAGE ADJUSTMENT

Offset voltage is adjusted with a  $20k\Omega$  potentiometer as shown in Figure 2. The potentiometer should be connected between pins 1 and 5 with its wiper connected to the V– supply. The typical trim range is  $\pm 4mV$ .

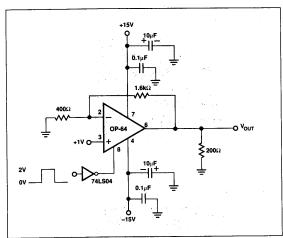

# **OP-64 DISABLE AMPLIFIER SHUTDOWN**

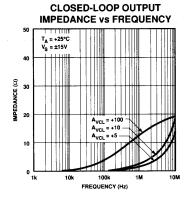

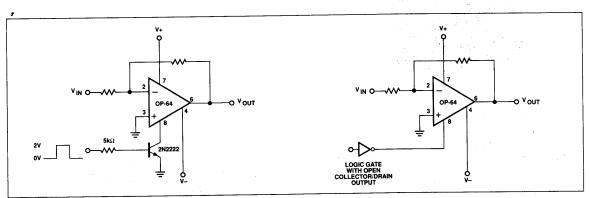

Pin 8 of the OP-64,  $\overline{DISABLE}$ , is an amplifier shutdown control input. The OP-64 operates normally when Pin 8 is left floating. When greater than 250 $\mu$ A is drawn from the  $\overline{DISABLE}$  pin, the OP-64 is disabled. The supply current drops to 1mA and the output impedance rises to 2k $\Omega$ . To draw current from the  $\overline{DISABLE}$  pin, an open collector output logic gate or a discrete NPN transistor can be used as shown in Figure 3. An internal resistor

FIGURE 4: DISABLE Turn-On/Turn-Off Test Circuit

limits the  $\overline{\text{DISABLE}}$  current to around 500 $\mu$ A if the  $\overline{\text{DISABLE}}$  pin is grounded with the OP-64 powered by  $\pm 15V$  supplies. These logic interface methods have the added advantage of level shifting the TTL signal to whatever supply voltage is used to power the OP-64.

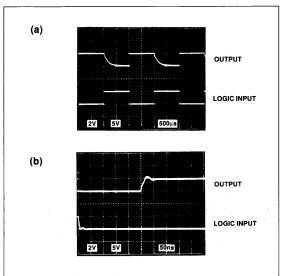

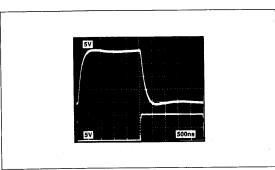

Figure 4 shows a test circuit for measuring the turn-on and turn-off times for the OP-64. The OP-64 is in a gain of 5 with a +1 V DC input. As the input pulse to the 74LS04 rises its output falls,

FIGURE 3: Simple circuits allow the OP-64 to be shut down.

ODED ATTONIAI ANIDI TETEBO (DI TETEBO

drawing current from the  $\overline{DISABLE}$  pin and disabling the amplifier. The output voltage delay is shown in Figure 5 and takes 500 $\mu$ s to reach ground due to the extra current supplied to the amplifier by the  $10\mu$ F electrolytic bypass capacitors. The turnon time is much quicker than the turn-off time. In this situation as the input to the 74LS04 falls its output rises, returning the OP-64 to normal operation. The amplifier's output turns on in 250ns.

FIGURE 5: (a) OP-64 turn-on and turn-off performance. (b) Expanded scale showing turn-on performance of the OP-64.

### **OVERDRIVE RECOVERY**

Figure 6 shows the overdrive recovery performance of the OP-64. Typical recovery time is 270ns from negative overdrive and 80ns from positive overdrive.

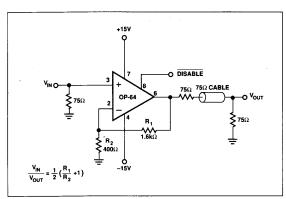

# **VIDEO AMPLIFIER/TERMINATED LINE DRIVER**

The OP-64 can be used as a video amplifier/terminated line driver as shown in Figure 8. With its high output current capability, the OP-64 eliminates the need for an external buffer.

FIGURE 6: OP-64 Overdrive Recovery

The  $75\Omega$  cable termination resistor minimizes reflections from the end of the cable. The  $75\Omega$  series output resistor absorbs any reflections caused by a mismatch between the  $75\Omega$  termination resistor and the characteristic cable impedance. In this circuit the output voltage,  $V_{\text{OUT}}$ , is one-half of the OP-64's output voltage due to the divider formed by the  $75\Omega$  terminating resistors. The output voltage at the end of the terminated cable,  $V_{\text{OUT}}$ , spans -1V to +1V. The differential gain and phase for the video amplifier is summarized in Table 1.

**TABLE 1:** Differential Gain and Phase of Video Amplifier/Line Driver

|                | Different | ial Gain | Differentia | l Phase |

|----------------|-----------|----------|-------------|---------|

| ٧ <sub>s</sub> | 3.58MHz   | 5MHz     | 3.58MHz     | 5MHz    |

| ±15V           | 0.008dB   | 0.016dB  | 0.03°       | 0.03°   |

| ±12V           | 0.008dB   | 0.018dB  | 0.03°       | 0.03°   |

FIGURE 7: Overdrive Recovery Test Circuit

FIGURE 8: Video Amplifier/Terminated Line Driver

FIGURE 9: Fast Transimpedance Amplifier

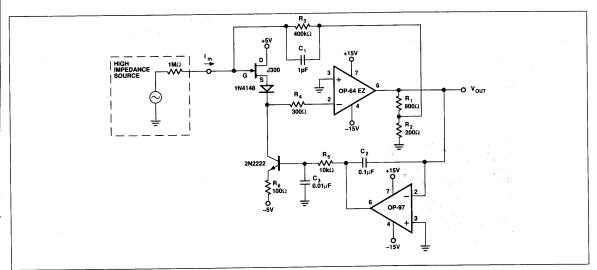

# **FAST TRANSIMPEDANCE AMPLIFIER**

The circuit shown in Figure 9 is a fast transimpedance amplifier designed to handle high speed signals from a high impedance source such as the output of a photomultiplier tube. The input current is amplified and converted to an output voltage by the transimpedance amplifier.

A JFET source-follower input is used to reduce the input bias current of the amplifier to 100 pA and lower the input current noise. Transimpedance of the amplifier is:

$$\frac{\sqrt[4]{OUT}}{I_{IN}} = \left(\frac{R_1}{R_2} + 1\right) R_3$$

and for the values shown equals

$$\frac{V_{OUT}}{I_{IN}} = \left(\frac{800\Omega}{200\Omega} + 1\right) 400k\Omega = 2V/\mu A$$

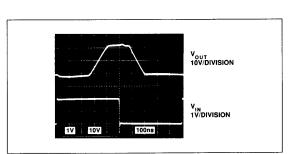

Figure 10 shows the output of the transimpedance amplifier when driven from a  $1M\Omega$  source impedance. The input signal of  $10\mu A_{p\cdot p}$  is converted into an output voltage of  $(10\mu A)~2V/\mu A=20V_{p\cdot p}$ . Output slew rate is  $100V/\mu s$ . The slew rate is limited by

the combination of the capacitance of the JFET gate with the  $1M\Omega$  source impedance. For best performance, the stray input capacitance should be kept as small as possible. The OP-97 is used in an integrator loop to reduce the total amplifier offset voltage to under  $25\mu V$ .

FIGURE 10: Output of the Fast Transimpedance Amplifier

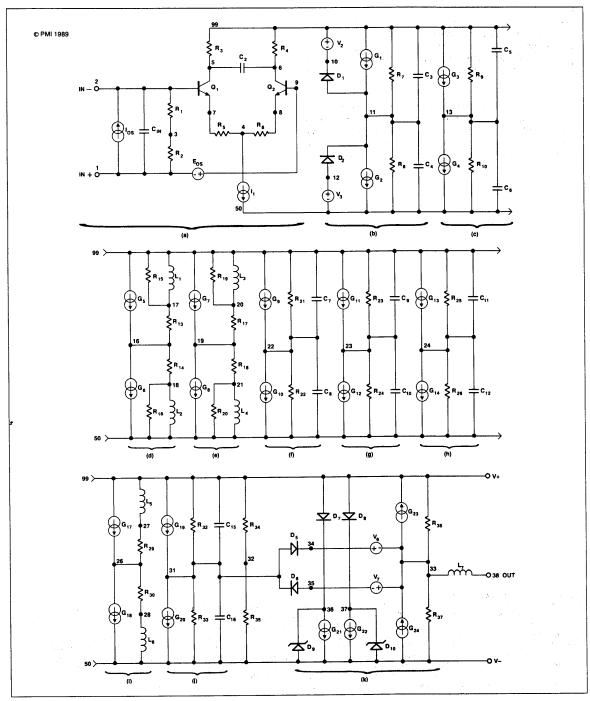

### **OP-64 SPICE MACRO-MODEL**

Figure 11 shows the node and net list for a SPICE macro-model of the OP-64. The model is a simplified version of the actual device and simulates important DC parameters such as  $V_{OS}$ ,  $I_{OS}$ ,  $I_{B}$ ,  $A_{VO}$ , CMR,  $V_{O}$  and  $I_{SY}$ . AC parameters such as slew rate, gain and phase response and CMR change with frequency are also simulated by the model

The model uses typical parameters for the OP-64. The poles and zeros in the model were determined from the actual open and closedloop gain and phase response of the OP-64. In this way the model presents an accurate AC representation of the actual device. The model assumes an ambient temperature of 25°C (see following pages).

### LICENSE STATEMENT AND LIMITED WARRANTY

This OP-64 macro-model is protected under United States copyright laws and California trade secret laws. Precision Monolithics Inc. hereby grants users of this macro-model, hereto referred to as the licensee, a nonexclusive, nontransferable license to use this OP-64 macro-model as long as the licensee abides by the terms of this agreement. Before using the OP-64 macro-model, the licensee should read this license. If the licensee does not accept these terms, this Data Sheet should be returned to PMI within 30 days.

The licensee agrees to treat this macro-model just like a book, except that the licensee may not loan, rent, lease, or license the macro-model, in whole, in part, or in modified form, to anyone outside the licensee's company. The licensee may modify this OP-64 macro-model to suit his specific applications, and the licensee may make copies of the macro-model for use within his company only.

This macro-model is provided solely and exclusively for use by PMI customers to assist them in the assessment of the OP-64 for possible applications. The OP-64 macro-model is provided "as is." PMI makes no warranty, either express or implied, including but not limited to any implied warranties or merchantability and fitness for a particular purpose using this macro-model. In no event will PMI be liable for special, collateral, incidental, or consequential damages in connection with or arising out of the use of the macro-model.

Although every effort has been made to ensure accuracy of the information contained in this application note, PMI assumes no responsibility for inadvertent errors. PMI reserves the right to make changes to the product and the macro-model without prior notice.

<sup>\*</sup> PSpice is a registered trademark of MicroSim Corporation.

<sup>\*\*</sup> HSPICE is a tradename of Meta-Software, Inc.

FIGURE 11a: OP-64 SPICE Macro-Model Schematic and Node List

```

OP-64 MACRO-MODEL @PMI 1989

*POLE AT 159 MHz

subckt OP-64 1 2 38 99 50

r23

1E6

23

23

INPUT STAGE & POLE AT 39.8 MHz

r24

50

1E6

c9

99

1E-15

c10 23

3

50

1E-15

g11 99

g12 23

r2

3

5E11

23

22 32 1E-6

г3

5

99

474.86

32 22 1E-6

50

6

г4

99

474.86

r5

4

423.26

*POLE AT 159 MHz

r6

8

423.26

cin

1

2

5E-12

r25

99

1E6

c2

6

r26

24

50

1E6

5

4.2106E-12

1E-15

c11

99

i1

4

50

1E-3

1E-7

c12 24

50

1E-15

ios

2

g13 99

poly(1) 26 32 4E-4 1

24

23 32 1E-6

9

eos

ğ14 24

50

32 23 1E-6

q1

5

qχ

q2

6

8

ďΧ

*COMMON-MODE GAIN NETWORK WITH ZERO AT 20kHz

* SECOND STAGE & POLE AT 3.8 kHz

r29

26

1E6

26

27

r30

I5

1E6

28

r7

7.1229E6

7.9575

99

7.1229E6

r8

11

50

16

28

50

7.9575

99

5.88E-12

c3

11

g17 99

26

33 32 1E-11

c4

11

50

poly(1) 5 6 4.31E-3 2.1059E-3

poly(1) 6 5 4.31E-3 2.1059E-3

2.25

5.88E-12

ğ18 26

50

32 33 1E-11

g1

g2

99

11

11

50

* POLE AT 159 MHz

v2

99

10

2.25

v3

12

50

r32

d1

10

dx

31

99

1E6

11

31

r33

50

1E6

d2

12

11

dx

c15

31

99

1E-15

c16 31

g19 99

* POLE AT 39.8 MHz

50

1E-15

31

24 32 1E-6

ğ20

31

50

32 24 1E-6

r9

13

99

1E6

r10

13

50

1E6

* OUTPUT STAGE

13

99

4E-15

С5

c6

13

50

4E-15

r34

20.0E3

g3

99

13

11 32 1E-6

r35

r36

32

33

50

20.0E3

ğ4

50

32 11 1E-6

60

99

r37

33

50

60

* ZERO-POLE PAIR AT 26.5 MHz /159 MHz

17

33

38

2.9E-7

31 33

g21

g22

36

33

16.666667E-3

50

r13

16

17

1E6

37

50

33

31

16.666667E-3

16

18

1E6

r14

ğ23

33

99

99

31

16.666667E-3

r15

17

99

5E6

50

34

33

33

35

ğ24

31

50

16.666667E-3

18

50

r16

5E6

v6

1.7

11

17

99

5.005E-3

33

٧7

1.7

12

50

5.005E-3

18

d5

31

34

dχ

g5

99

16

13 32 1E-6

ģ6

d6

35

31

16

50

32 13 1E-6

dx

99

d7

36

ďχ

d8

99

37

dx

* ZERO-POLE PAIR AT 31.8 MHz / 39.8 MHz

d9

50

36

dy

d10 50

r17

19

1E6

37

dy

20

r18

19

21

1E6

* MODELS USED

r19

20

99

2.5157E5

21

50

2.5157E5

r20

•model qx NPN(BF=2500)

20

13

99

1.006E-3

•model dx D(IS=1E-15)

14

21

50

1.006E-3

·model dy

D(IS=1E-15 BV=50)

99

19

16 32 1E-6

g7

ends OP-64

ģ8

19

50

32 16 1E-6

* POLE AT 100 MHz

22

22

r21

99

1E6

r22

50

1E6

22

99

1.59E-15

c7

22

99

с8

50

1.59E-15

g9

22

19 32 1E-6

ğ10

22

50

32 19 1E-6

```

FIGURE 11b: OP-64 SPICE Net-List