Differential Analog Input

# INTEGRATING CONVERTER ANALOG PROCESSORS

### **FEATURES**

| _ | Differential Arialog Input                            |

|---|-------------------------------------------------------|

|   | Differential Reference                                |

|   | Low Linearity Error0.003%                             |

|   | Fast Zero-Crossing Comparator4 μs                     |

|   | Low Power Dissipation10 mW                            |

| • | Auto-Zero Cycle Eliminates Zero-Scale Error and Drift |

|   | Zero Integrator Phase Speeds Recovery From            |

|   | Overrange Input Signals                               |

|   | Automatic Internal Polarity Detection                 |

|   | Low Input Current15 pA Max                            |

|   | Wide Analog Input Voltage±4.2V                        |

|   | Microprocessor Control of Dual-Slope ADC              |

Resolution ...... Up to 16 Bits + Sign (TC500A)

### IMPROVED PERFORMANCE

The TC500A is an improved version of the popular TC500. The improvements allow up to 16 bits of resolution (plus sign) or faster conversion times for lower resolution applications.

### **GENERAL DESCRIPTION**

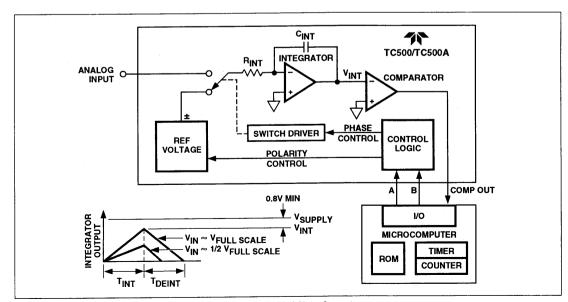

The CMOS TC500/TC500A contain all the analog circuits needed to construct an integrating analog-to-digital converter. The analog input buffer, integrator, analog switches, comparator and phase control logic are all on chip.

The dual-slope converter uses time to quantize the analog input signal. A microprocessor and software routine perform the digital function of "counting clocks" for the dual-slope integrating converter process. The user can control resolution and conversion speed through software. The TC500/TC500A analog building block can be used to construct a fast or high-resolution converter by modifying software routines.

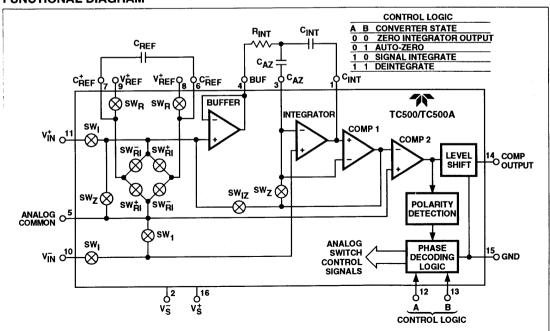

### **FUNCTIONAL DIAGRAM**

Conversion

# INTEGRATING CONVERTER ANALOG PROCESSORS

# TC500 TC500A

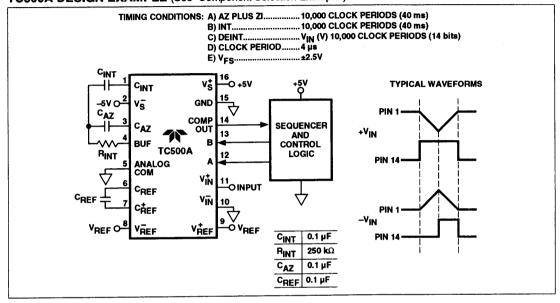

A microprocessor controls the TC500/TC500A through the A and B logic input signals. Four phases are possible: auto-zero, signal integrate, reference integrate (deintegrate), and integrator zero output.

The TC500/TC500A comparator's output provides polarity and integrator zero-crossing information. The comparator output is always low when the integrator crosses zero during the deintegrate phase. This signals the end of a conversion to the processor.

A precision, dual-slope integrating converter with automatic zero-scale offset voltage and drift correction requires only a reference, three capacitors, a resistor and a controller. The TC500/TC500A contain the analog circuits needed

to construct a dual-slope integrating converter with an auto zero phase. A zero-integrator output phase can be selected to eliminate errors caused by out-of-range input signals. The zero-integrator phase greatly improves recovery after an overrange conversion

The CMOS TC500/TC500A operate from ±5V supplies. Power dissipation is only 10 mW. Leakage currents at the differential inputs are a low 10 pA. The TC500/TC500A differential reference inputs allow easy ratiometric measurements.

Although the TC500A is pin-for-pin compatible with the TC500, some programming constraints are imposed. (See "Integrator Output Zero.")

### **ORDERING INFORMATION**

| Part No.  | Package            | Temperature Range | System Resolution     |

|-----------|--------------------|-------------------|-----------------------|

| TC500ACPE | 16-Pin Plastic DIP | 0°C to +70°C      | 16-Bit (30 ppm)       |

| TC500AIJE | 16-Pin CerDIP      | -25°C to +85°C    | 16-Bit (30 ppm)       |

| TC500ACOE | 16-Pin SO          | 0°C to +70°C      | 16-Bit (30 ppm)       |

| TC500CPE  | 16-Pin Plastic DIP | 0°C to +70°C      | 4-1/2 Digits (50 ppm) |

| TC500IJE  | 16-Pin CerDIP      | -25°C to +85°C    | 4-1/2 Digits (50 ppm) |

| TC500COE  | 16-Pin SO          | 0°C to +70°C      | 4-1/2 Digits (50 ppm) |

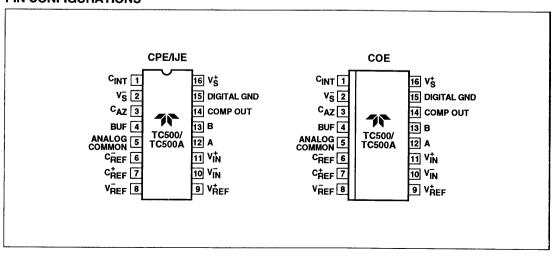

### **PIN CONFIGURATIONS**

# INTEGRATING CONVERTER ANALOG PROCESSORS

TC500 TC500A

### **ABSOLUTE MAXIMUM RATINGS**

| Supply (V <sub>S</sub> <sup>+</sup> to V <sub>S</sub> <sup>-</sup> )+18V                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| Positive Supply Voltage (Vs+ to GND)+12V                                                                                                       |

| Negative Supply Voltage (V <sub>S</sub> <sup>-</sup> to GND)12V                                                                                |

| Analog Input Voltage (V <sub>IN</sub> <sup>+</sup> or V <sub>IN</sub> <sup>-</sup> )V <sub>S</sub> <sup>+</sup> to V <sub>S</sub> <sup>-</sup> |

| Logic Input VoltageV <sub>S</sub> + +0.3V to GND -0.3V                                                                                         |

| Package Power Dissipation0.5W                                                                                                                  |

| Ambient Operating Temperature Range                                                                                                            |

| Plastic Package (C)0°C to +70°C                                                                                                                |

| CerDIP Package (I)25°C to +85°C                                                                                                                |

| Storage Temperature Range         | 65°C to +150°C |

|-----------------------------------|----------------|

| Lead Temperature (Soldering, 60 s | ec)+300°C      |

Static-sensitive device. Unused devices must be stored in conductive material. Protect devices from static discharge and static fields. Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may effect device reliability.

# **ELECTRICAL CHARACTERISTICS:** $T_A = +25$ °C, $V_S = \pm 5$ V, unless otherwise specified. $C_{AZ} = C_{REF} = 0.1~\mu F$ .

|                  |                                                |                                                                    | TC500                            |       |                       | TC500A                           |       |                       |                   |

|------------------|------------------------------------------------|--------------------------------------------------------------------|----------------------------------|-------|-----------------------|----------------------------------|-------|-----------------------|-------------------|

| Symbol           | Parameter                                      | <b>Test Conditions</b>                                             | Min                              | Тур   | Max                   | Min                              | Тур   | Max                   | Unit              |

| Analog           |                                                |                                                                    |                                  |       |                       |                                  |       |                       |                   |

|                  | Resolution                                     | Note 1                                                             | _                                | _     | 50                    | _                                | _     | 30                    | ppm               |

| ZSE              | Zero-Scale Error                               | Note 1                                                             | _                                | _     | 0.005                 | _                                | -     | 0.003                 | %                 |

| ENL              | End Point Linearity                            | Note 1                                                             | _                                | 0.005 | 0.01                  | <u> </u>                         | 0.005 | 0.01                  | %                 |

| NL               | Best Case Straight<br>Line Linearity           | Notes 1 and 2                                                      |                                  | _     | 0.005                 | _                                |       | 0.003                 | %                 |

| DNL              | Differential Nonlinearity                      |                                                                    | _                                | _     | 0.0025                | <del>-</del>                     | _     | 0.0025                | %                 |

| TCzs             | Zero-Scale<br>Temperature<br>Coefficient       | Over Operating<br>Temperature Range                                | _                                | 1     | 2                     |                                  | 1     | 2                     | μV/°C             |

| SYE              | Full-Scale Symmetry<br>Error (Roll-Over Error) |                                                                    | -                                | _     | 0.01                  | _                                | _     | 0.006                 | %                 |

|                  | Ratiometric Reading                            | V <sub>IN</sub> = V <sub>REF</sub> = 1V                            | -                                | _     | 0.035                 | _                                | 1     | 0.035                 | %                 |

| FS <sub>TC</sub> | Full-Scale Temperature<br>Coefficient          | Over Operating. Temperature Range External Reference TC = 0 ppm/°C | _                                |       | 10                    | _                                | _     | 10                    | ppm/°C            |

| I <sub>IN</sub>  | Input Current                                  | $V_{IN} = 0V$                                                      | -                                | 6     | 15                    | _                                | 6     | 15                    | pΑ                |

| CMRR             | Common-Mode<br>Rejection Ratio                 | -1V ≤ V <sub>CM</sub> ≤ 1V                                         | _                                | 80    | _                     | _                                | 80    | _                     | dB                |

| V <sub>CMR</sub> | Common-Mode<br>Voltage Range                   | V <sub>S</sub> = ±5V                                               | V <sub>S</sub> <sup>-</sup> +1.5 | _     | V <sub>S</sub> + –1.5 | V <sub>S</sub> <sup>-</sup> +1.5 |       | V <sub>S</sub> + –1.5 |                   |

|                  | Integrator Output Swing                        | $V_S = \pm 5V$                                                     | <b>—</b>                         | _     | ±4.1                  | _                                | _     | ±4.1                  | ٧                 |

|                  | Analog Input Signal Range                      |                                                                    | V <sub>S</sub> -+0.8             | _     | V <sub>S</sub> + -0.8 | V <sub>S</sub> <sup>-</sup> +0.8 | _     | V <sub>S</sub> + -0.8 | ٧                 |

| e <sub>N</sub>   | Noise                                          | $V_{IN} = 0V$                                                      |                                  | 30    |                       |                                  | 30    |                       | μV <sub>P-P</sub> |

| Digital          |                                                |                                                                    |                                  |       |                       |                                  |       |                       |                   |

|                  | Reference Input Signal<br>Range                |                                                                    | V <sub>S</sub> -+1               | _     | V <sub>S</sub> + -1   | V <sub>S</sub> -+1               |       | V <sub>S</sub> + -1   | ٧                 |

| V <sub>OH</sub>  | Comparator Logic 1,<br>Output High             | I <sub>SOURCE</sub> = 800 μA                                       | 4                                | _     |                       | 4                                |       |                       | V                 |

| V <sub>OL</sub>  | Comparator Logic 0,<br>Output Low              | I <sub>SINK</sub> = 4 mA                                           |                                  | _     | 0.4                   |                                  |       | 0.4                   | V                 |

| V <sub>IH</sub>  | Logic 1, Input High Voltage                    |                                                                    | 3.5                              | _     | _                     | 3.5                              | _     | _                     | ٧                 |

| V <sub>IL</sub>  | Logic 0, Input Low Voltage                     |                                                                    |                                  | _     | 1                     |                                  | _     | 1                     | ٧                 |

| IL               | Logic Input Current                            | Logic 1 or 0                                                       | _                                | 0.05  | _                     | _                                | 0.05  |                       | μΑ                |

| t <sub>D</sub>   | Comparator Delay                               |                                                                    | _                                | 4     | _                     | _                                | 4     | _                     | μs                |

# TC500 TC500A

### **ELECTRICAL CHARACTERISTICS (Cont.)**

|                                   | Parameter                                  | Test Conditions              | TC500 |     |     | TC500A |     |     | T    |

|-----------------------------------|--------------------------------------------|------------------------------|-------|-----|-----|--------|-----|-----|------|

| Symbol                            |                                            |                              | Min   | Тур | Max | Min    | Тур | Max | Unit |

| Power                             |                                            |                              |       |     |     |        |     |     |      |

| Is                                | Supply Current                             | $V_S = \pm 5V, A = 1, B = 1$ | _     | 1   | 1.5 | _      | 1   | 1.5 | mA   |

| PD                                | Power Dissipation                          | $V_S = \pm 5V$               | _     | _   | 15  | _      | T — | 15  | mW   |

| V <sub>S</sub> +                  | Positive Supply Operating Voltage Range    |                              | 4     | -   | 10  | 4      | _   | 10  | ٧    |

| V <sub>S</sub> -                  | Negative Supply<br>Operating Voltage Range |                              | -3    | _   | -8  | -3     | -   | -8  | ٧    |

| V <sub>S</sub> +-V <sub>S</sub> - | Supply Operating<br>Voltage Range          |                              | 7     | -   | 15  | 7      | -   | 15  | ٧    |

NOTES: 1. Integrate time ≥200 ms, auto-zero time ≥100 ms, V<sub>INT</sub> (peak) ≈ 4V.

2. End point linearity at ±1/4, ±1/2, ±3/4 FS after full-scale adjustment.

### OPERATIONAL THEORY

The TC500 and TC500A are dual-slope, integrating analog processors which are used with a microprocessor to generate analog-to-digital conversions of up to 16 bits of resolution. Although the TC500 and TC500A are virtually the same, the TC500A is recommended for applications requiring more than 14 bits of resolution.

The TC500 and TC500A incorporate a system zero phase and integrator output voltage zero phase, in addition to the normal two-phase, dual-slope measurement cycle. Reduced system errors, fewer calibration steps, and shorter overrange recovery time result.

The TC500 and TC500A measurement cycle can use all four phases, if desired.

- (1) Auto zero

- (2) Analog input signal integration

- (3) Reference voltage integration (deintegrate)

- (4) Integrator output zero

Internal analog gate status is shown in Table I for each phase (see the functional diagram).

### Auto-Zero Phase

During this phase, errors due to buffer, integrator and comparator offset voltages are compensated for by charging  $C_{AZ}$  (auto-zero capacitor) with a compensating error voltage.

The external input signal is disconnected from the internal circuitry by opening the two SW<sub>I</sub> switches. The internal input points connect to analog common. The reference capacitor charges to the reference voltage potential through SW<sub>R</sub>. A feedback loop, closed around the integrator and comparator, charges the C<sub>AZ</sub> capacitor with a voltage to compensate for buffer amplifier, integrator and comparator offset voltages.

### **Analog Input Signal Integration Phase**

The TC500/TC500A integrate the differential voltage between the (+) and (-) inputs. The differential voltage must be within the device's common-mode range.

The input signal polarity is normally checked via software at the end of this phase.

Table I. Internal Analog Gate Status

|                          | Internal Analog Gate Status |                    |                                         |        |        |                 |        |  |

|--------------------------|-----------------------------|--------------------|-----------------------------------------|--------|--------|-----------------|--------|--|

| Conversion Phase         | SWI                         | SW <sub>RI</sub> + | SW <sub>RI</sub> -                      | SWz    | SWR    | SW <sub>1</sub> | SWiz   |  |

| Auto-Zero (A=0, B=1)     |                             |                    |                                         | Closed | Closed | Closed          |        |  |

| Input Signal Integration | Closed                      |                    |                                         |        |        |                 |        |  |

| (A=1, B=0)               |                             |                    |                                         |        |        |                 |        |  |

| Reference Voltage        |                             | Closed*            |                                         |        |        | Closed          |        |  |

| Deintegration (A=1, B=1) |                             |                    |                                         |        |        |                 |        |  |

| Integrator Output Zero   |                             |                    | *************************************** |        | Closed | Closed          | Closed |  |

| (A=0, B=0)               |                             |                    |                                         |        |        |                 |        |  |

<sup>\*</sup>Assumes a positive polarity input signal. SW<sub>RI</sub> would be closed for a negative input signal.

# **Reference Voltage Deintegration Phase**

The previously charged reference capacitor is connected with the proper polarity to ramp the integrator output back to zero.

### Integrator Output Zero Phase

This phase guarantees the integrator output is at 0V when the system zero phase is entered and that the true system offset voltages are compensated. This phase is used at the end of the reference voltage deintegration (DEINT) phase and SHOULD be used for all TC500/TC500A applications. This phase MUST be used for resolutions of more than 14 bits. If this phase is not used, the value of the auto-zero capacitor (CAZ) must be about 23 the value of the integration capacitor (CINT) to reduce the effects of charge-sharing. The integrator output zero phase should be programmed to operate until the output of the comparator returns "high" (1) or for fixed time of about 2 ms.

### ANALOG SECTION

# Differential Inputs (V<sub>IN</sub>+ [Pin 11], V<sub>IN</sub>- [Pin 10])

The TC500/TC500A operate with differential voltages within the input amplifier common-mode range. The input amplifier common-mode range extends from 0.8V below positive supply to 0.8V above negative supply. Within this common-mode voltage range, a common-mode rejection is typically 80 dB. Full accuracy is maintained, however, when the inputs are no less than 1.5V from either supply.

The integrator output also follows the common-mode voltage. The integrator output must not be allowed to saturate. A worst-case condition exists, for example, when a large, positive common-mode voltage with a near full-scale negative differential input voltage is applied. The negative input signal drives the integrator positive when most of its swing has been used up by the positive common-mode voltage. For these critical applications, the integrator swing can be reduced. The integrator output can swing within 0.9V of either supply without loss of linearity.

# Analog Common (Pin 5)

Analog common is used as  $V_{IN}$  return during systemzero and reference deintegrate. If  $V_{IN}^-$  is different from analog common, a common-mode voltage exists in the system. This signal is rejected by the excellent CMRR of the converter. In most applications,  $V_{IN}^-$  will be set at a fixed known voltage (i.e., power supply common). A common-mode voltage will exist when  $V_{IN}^-$  is not connected to analog common.

### **Differential Reference**

$(V_{REF}^+[Pin 9], V_{REF}^-[Pin 8])$

The reference voltage can be generated anywhere within 1V of the power supply voltage of the converter. Rollover error is caused by the reference capacitor losing or gaining charge due to stray capacitance on its nodes. The difference in reference for (+) or (-) input voltages will cause a roll-over error. This error can be minimized by using a large reference capacitor in comparison to the stray capacitance.

# Phase Control Inputs (A [Pin 12], B [Pin 13])

The A, B unlatched logic inputs select the TC500/TC500A operating phase. The A, B inputs are normally driven by a microprocessor I/O port or peripheral I/O chip.

# **Comparator Output**

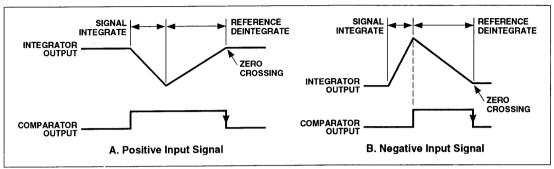

By monitoring the comparator output during the fixedsignal integrate time, the input signal polarity can be determined by the microprocessor controlling the conversion. The comparator output is high for positive signals and low for negative signals during the signal-integrate phase.

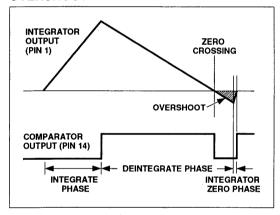

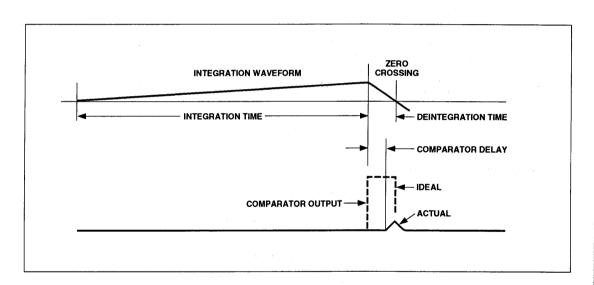

During the reference deintegrate phase, the comparator output will make a high-to-low transition as the integrator output ramp crosses zero. The transition is used to signal the processor that the conversion is complete.

The internal comparator delay is 4 us, typically.

Figure 1 shows the comparator output for large positive and negative signal inputs. For signal inputs at or near zero volts, however, the integrator swing is nonexistent. If common-mode noise is present, the comparator can switch several times during the signal-integrate period. To ensure that the polarity reading is correct, the comparator output should be read and stored at the end of signal integrate.

A "low" (0) on the TC500/TC500A comparator, during the deintegrate phase, signals the processor that the conversion is complete.

The comparator output is undefined during the autozero and the integrator output zero phases.

# GENERAL THEORY OF OPERATION Dual-Slope Conversion Principles

The TC500 is an integrating analog-to-digital converter building block. An understanding of the dual-slope conversion technique will aid in following the detailed TC500A operation theory.

The conventional dual-slope converter measurement cycle has two distinct phases:

- Input signal integration

- (2) Reference voltage integration (deintegration)

### TC500 TC500A

Figure 1. Comparator Output

The input signal being converted is integrated for a fixed time period, measured by counting clock pulses. An opposite polarity constant reference voltage is then integrated until the integrator output voltage returns to zero. The TC500/TC500A automatically switch in the proper polarity reference signal. The reference integration time is directly proportional to the input signal (Figure 2).

In a simple dual-slope converter, a complete conversion requires the integrator output to "ramp-up" and "ramp-down." The TC500/TC500A comparator zero-crossing signals the processor to indicate the deintegrate cycle is complete.

A simple mathematical equation relates the input signal, reference voltage and integration time:

$$\frac{1}{R_{INT}\,C_{INT}}\,\,\int_{0}^{t_{INT}}\,V_{IN}\left(t\right)\,dt = \,\frac{V_{REF}\,t_{DEINT}}{R_{INT}\,C_{INT}}$$

where:

V<sub>RFF</sub> = Reference voltage

t<sub>INT</sub> = Signal integration time (fixed)

t<sub>DEINT</sub> = reference voltage integration time (variable)

Figure 2. Basic Dual-Slope Converter

# INTEGRATING CONVERTER ANALOG PROCESSORS

TC500 TC500A

For a constant V<sub>IN</sub>:

$$V_{IN} = V_{REF} \frac{t_{DEINT}}{t_{INT}}$$

The dual-slope converter accuracy is unrelated to the integrating resistor and capacitor values as long as they are stable during a measurement cycle.

An inherent benefit is noise immunity. Input noise spikes are integrated or averaged to zero during the integration periods. Integrating ADCs are immune to the large conversion errors that plague succesive approximation converters in high-noise environments.

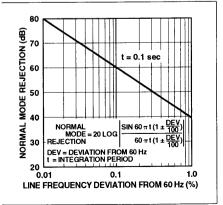

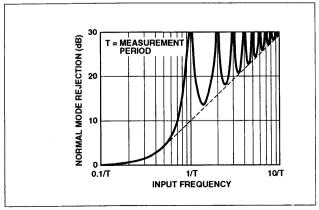

Integrating converters provide noise rejection automatically with at least a 20-dB/decade attenuation rate. Interference signals with frequencies at integral multiples of the integration period are, theoretically, completely removed. This intuitively makes sense, since the average value of a sine wave of frequency (1/t) averaged over a period (t) is zero.

Integrating converters often establish the integration period to reject 50/60 Hz line frequency interference signals. The ability to reject such signals is shown by a normal mode rejection plot (Figure 3). Normal mode rejection is practically set to 50 to 65 dB, since the line frequency can deviate by a few tenths of a percent (Figure 4).

### Criteria for CAZ and CREF

$$C_{AZ} \approx C_{REF} \approx \frac{2^{N} t_{INT} \left(V_{INT} + V_{REF}\right) I_{LEAKAGE}}{V_{INT} \, V_{REF}}$$

where:

N = resolution (bits)

I<sub>LEAKAGE</sub> ≈ 15 pA V<sub>INT</sub> (see Figure 2)

Figure 3. Normal Mode Rejection vs Input Frequency

This equation is for reference only. Use 0.1  $\mu F$  capacitor for all applications that have 8 or more conversions per second. Use a 0.22  $\mu F$  capacitor for 3 to 7 conversions per second, and a 0.47  $\mu F$  capacitor for 2 or less conversions per second.

# COMPONENT VALUE SELECTION

### Integrating Resistor (RINT)

The desired full-scale input voltage and output current capability of the input buffer and integrator amplifier set the integration resistor value. The internal class A output stage amplifiers will supply a 20- $\mu$ A drive current with minimal linearity error.  $R_{INT}$  is easily calculated for a 20- $\mu$ A full-scale current:

$$R_{INT}$$

(M $\Omega$ ) =  $\frac{Full-Scale Input Voltage (V)}{20}$  ±20%

For loop stability,  $R_{INT}$  should be  $\geq 50$  k $\Omega$ .

# Reference Capacitor (CREF)

A 0.1-μF capacitor is suggested. Larger values may be used to limit roll-over errors. Low leakage capacitors (such as polypropylene) are required.

# Auto-Zero Capacitor (CAZ)

A  $0.1-\mu F$  polypropylene capacitor is suggested.

Figure 4. Intregrating Converter Normal Mode Rejection vs 60 Hz Line Frequency Variations

# TC500 TC500A

# Integrating Capacitor (C<sub>INT</sub>)

The integrating capacitor should be selected to maximize integrator output swing. The integrator output will swing to within 0.8V of  $V_S^+$  or  $V_S^-$  without saturating.

Using the suggested 20-µA full-scale buffer output current, the integrating capacitor is easily calculated:

$$C_{INT} = \frac{(t_{INT}) (V_{FS})}{(V_{INT}) (R_{INT})} \approx 5 t_{INT} (\mu F)$$

where:

t<sub>INT</sub> = Integration period

V<sub>FS</sub> = Full-scale input voltage

V<sub>INT</sub> = Integrator output voltage swing

A very important integrating capacitor characteristic is dielectric absorption. Polypropylene capacitors give undetectable errors at reasonable cost. Polyester and polycarbonate capacitors may also be used in less critical applications.

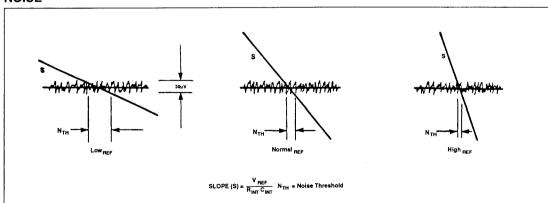

The threshold noise ( $N_{TH}$ ) is the algebraic sum of the integrator noise and the comparator noise. This value is typically about 30  $\mu$ V. The graph shows how the value of the reference voltage can influence the results of the final count.

Errors caused by the low-frequency buffer noise may be reduced by increased integration times.

# Signal-to-Noise Ratio

S/N (dB) = 20 Log

$$\left(\frac{V_{IN}}{30 \,\mu\text{V}} \cdot \frac{t_{INT}}{R_{INT} \cdot C_{INT}}\right)$$

The maximum performance of the TC500/TC500A require that overshoot at the end of the deintegration phase be minimized. Also, the integrator zero phase may be terminated as soon as the comparator output returns to "high" (1).

### **OVERSHOOT**

### NOISE

# TC500A DESIGN EXAMPLE (See "Component Selection Example")

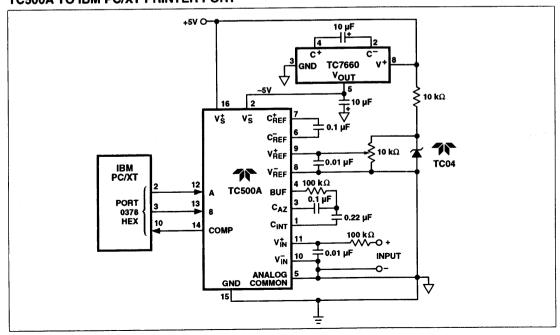

### TC500A TO IBM PC/XT PRINTER PORT

### Interrupt Operation

The comparator output stays low during the Integration phase (A=1, B=0) whenever the input polarity is negative. In those cases where the input polarity is negative AND very near zero, the zero-crossing occurs before the comparator has had a chance to go positive. Thus, no negative-edge will be generated and the microprocessor will not be interrupted.

With a negative input voltage very near zero, the output of the comparator does not have enough time to get full positive. This anomaly is caused by the comparator delay and rise time limitations.

One solution to overcome this condition is to have the microprocessor monitor the comparator output. It can then end the deintegration phase as soon as it sees a zero.

Another solution is to have the microprocessor enable the interrupt and look at the comparator output. If the output is high, the interrupt will be properly triggered. If the output is low, end the deintegration phase and disable the interrupt

Either solution will produce reliable low voltage conversions.

### Rate of Conversion

The conversion times for the TC500/TC500A are a function of many variables and constants. The dominate component is CINT:

> Conversion Time (sec) =  $0.4 \times C_{INT} (\mu F) \times (2 + (V_{IN}/V_{REF}))$

The assumptions for this equation are suggested but not strictly required. They are:

> Auto-zero time  $(T_{A7})$  = Integration time  $(T_{NT})$ Peak integration voltage (V<sub>INT</sub>) = 4V Maximum buffer current  $(V_{IN(MAX)}/R_{INT}) = 20 \mu A$

# Component Selection Example

Known: 1) Supply voltage for TC500A

(V<sub>SUP</sub>) 2) Maximum input voltage  $(V_{IN(MAX)})$ 3) Integration time  $(T_{INT})$ 4) Output resolution (bits) (N) 5) Clock period (tclock)

Assume:  $V_{SUP} = \pm 5V$

$t_{CLOCK} = 4 \mu s$

$V_{SUP} = |V_{SUP}|$  $V_{IN(MAX)} = \pm 2.5V$  $V_{IN(MAX)} = IV_{IN(MAX)}I$  $T_{INT} = 40 \text{ ms}$ N = 14 bits

# INTEGRATING CONVERTER **ANALOG PROCESSORS**

$$R_{INT} = \frac{V_{IN(MAX)}}{I_{BUF(MAX)}}$$

Where I<sub>BUF(MAX)</sub> ≈ 20 μA

$$R_{INT} = \frac{2.5V}{20 \,\mu\text{A}} = 125K$$

Use 130K

$$\therefore \ I_{BUF} = \frac{2.5V}{130K} = 19.2 \ \mu\text{A}$$

$$C_{INT} = \frac{T_{INT} I_{BUF(MAX)}}{V_{INT}}$$

Where  $V_{INT} = V_{SUP} - 1V = 4V$

$$C_{INT} = \frac{40 \text{ ms } 19.2 \, \mu\text{A}}{4\text{V}} = 0.192 \, \mu\text{F}$$

Use 0.2 uF

# Step 3: Calculate V<sub>REF</sub>

$$V_{REF} = \frac{V_{INT} C_{INT} R_{INT}}{T_{DEINT}}$$

Where T<sub>DEINT</sub> = 2<sup>N</sup> t<sub>CLOCK</sub>

$$V_{REF} = \frac{4V \cdot 0.2 \ \mu F \cdot 130 K}{2^N \ t_{CLOCK}} = 1.587...V$$

$$K_{INT} = \frac{T_{INT}}{t_{CLOCK}}$$

Where R<sub>INT</sub>

$$\frac{40 \text{ ms}}{4 \mu \text{s}} = 10,000 \text{ Counts}$$

**Results:**

$$K_{DEINT} = V_{IN} \frac{K_{INT}}{V_{RFF}} = V_{IN} \frac{10,000}{1.587...V}$$

Where

$$K_{DEINT}$$

= Number of clock periods during  $T_{DEINT}$

### Normalization

The reference voltage can be adjusted to scale the deintegrate count to be directly equivalent to the input voltage.

$\frac{K_{INT}}{V_{RFF}}$  = Counts/Volt Since:

If: V<sub>RFF</sub> is adjusted such that

$V_{REF} = \frac{10000 \text{ Counts}}{10000 \text{ Counts/Volt}} = \frac{K_{INT}}{10000 \text{ Counts/Volt}} = 1V$

$K_{DEINT} = \frac{V_{IN}}{100 \,\mu V}$  and N ≈ 14.61 Bits Then:

If KDEINT = 18357 Counts, e.g., then  $V_{IN} = 1.8357V$

### **BONDING DIAGRAM**