A Schlumberger Company

## μA685 High Speed Single Latched Comparator

Linear Division Comparators

## Description

The  $\mu$ A685 is a fast voltage comparator manufactured with an advanced high speed bipolar process that makes possible very short propagation delays without sacrificing the excellent matching characteristics formerly associated only with slow, high performance linear ICs. The circuit has differential analog inputs and complementary logic outputs compatible with most forms of ECL. The output current capability is adequate for driving terminated 50  $\Omega$  transmission lines. The low input offset and high resolution make this comparator especially suitable for high speed precision analog to digital processing.

A latch function is provided to allow the comparator to be used in a sample and hold mode. If the latch enable is HIGH, the comparator functions normally. When the latch enable is driven LOW, the comparator outputs are locked in their existing logical states. If the latch function is not used, the latch enable must be connected to ground.

The  $\mu$ A685 is lead compatible with the AM685.

- 6.5 ns Maximum Propagation Delay At 5.0 mV Overdrive

- 3.0 ns Latch Set up Time

- Complementary ECL Outputs

- 50 Ω Line Driving Capability

- Typical Output Skew 0.2 ns

- Constant Propagation Delay With Overdrive

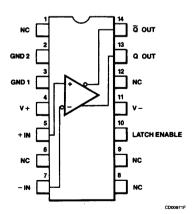

Connection Diagram SO-14 Package (Top View)

Order Information

Device Code Package Code

µA685SV KD

Package Description

Molded Surface Mount

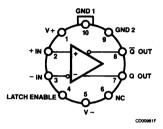

## Connection Diagram 10-Lead Metal Package (Top View)

| Order Information |              |                     |  |  |  |  |  |

|-------------------|--------------|---------------------|--|--|--|--|--|

| Device Code       | Package Code | Package Description |  |  |  |  |  |

| μA685HM           | 5X           | Metal               |  |  |  |  |  |

| μA685HV           | 5X           | Metal               |  |  |  |  |  |

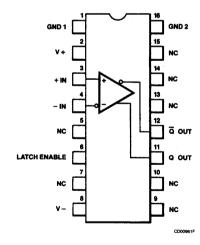

## Connection Diagram 16-Lead DIP (Top View)

| Order Information |              |                     |  |  |  |  |

|-------------------|--------------|---------------------|--|--|--|--|

| Device Code       | Package Code | Package Description |  |  |  |  |

| μA685DM           | 6B           | Ceramic DIP         |  |  |  |  |

| μA685DV           | 6B           | Ceramic DIP         |  |  |  |  |

| μA685PV           | 9B           | Molded DIP          |  |  |  |  |

| Absolute Maximum Ratings    |                 |

|-----------------------------|-----------------|

| Storage Temperature Range   |                 |

| Metal Can and Ceramic DIP   | -65°C to +175°C |

| Molded DIP and SO-14        | -65°C to +150°C |

| Operating Temperature Range |                 |

| Extended (µA685M)           | 55°C to +125°C  |

| Industrial (µA685V)         | -30°C to +85°C  |

| Lead Temperature            |                 |

| Metal Can and Ceramic DIP   |                 |

| (soldering, 60 s)           | 300°C           |

| Molded DIP and SO-14        |                 |

| (soldering, 10 s)           | 265°C           |

| Internal Power Dissipation <sup>1, 2</sup> |        |

|--------------------------------------------|--------|

| 10L-Metal Can                              | 1.07 W |

| 16L-Ceramic DIP                            | 1.50 W |

| 16L-Molded DIP                             | 1.04 W |

| SO-14                                      | 0.93 W |

| Positive Supply Voltage                    | +7.0 V |

| Negative Supply Voltage                    | -7.0 V |

| Input Voltage                              | ±4.0 V |

| Differential Input Voltage                 | ±6.0 V |

| Output Current                             | 30 mA  |

| Minimum Operating Voltage (V+ to V-)       | 9.7 V  |

|                                            |        |

#### Notes

- 1.  $T_{\rm J~Max}$  = 150°C for the Moided DIP and SO-14, and 175°C for the Metal Can and Ceramic DIP.

- Ratings apply to ambient temperature at 25°C. Above this temperature, derate the 10L-Metal Can at 7.1 mW°C, the 16L-Ceramic DIP at 10 mW/°C, the 16L-Molded DIP at 8.3 mW/°C, and the SO-14 at 7.5 mW/°C.

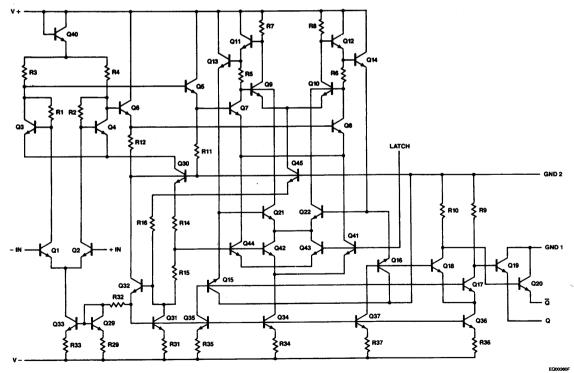

## **Equivalent Circuit**

$\mu$ A685

Electrical Characteristics Over recommended operating temperature and supply voltage ranges, unless otherwise specified.

## **DC** Characteristics

|                          |                                                                      |                                                       | μΑθ    | 885V   | μ <b>Α</b> 6 | 85M    |       |

|--------------------------|----------------------------------------------------------------------|-------------------------------------------------------|--------|--------|--------------|--------|-------|

| Symbol                   | Characteristic                                                       | Condition <sup>2</sup>                                | Min.   | Max.   | Min.         | Max.   | Units |

| V <sub>IO</sub>          | Input Offset Voltage                                                 | $R_S \le 100 \Omega$ , $T_A = 25$ °C                  | -2.0   | +2.0   | -2.0         | +2.0   | mV    |

|                          |                                                                      | R <sub>S</sub> ≤100 Ω                                 | -2.5   | +2.5   | -3.0         | +3.0   |       |

| $\Delta V_{IO}/\Delta T$ | Average Temperature Coefficient of Input Offset Voltage <sup>3</sup> | R <sub>S</sub> ≤100 Ω                                 | -10    | +10    | -10          | +10    | μV/°C |

| I <sub>IO</sub>          | Input Offset Current <sup>3</sup>                                    | 25°C ≤ T <sub>A</sub> ≤ T <sub>A Max</sub>            | -1.0   | +1.0   | -1.0         | +1.0   | μΑ    |

|                          |                                                                      | T <sub>A</sub> = T <sub>A Min</sub>                   | -1.3   | +1.3   | -1.6         | +1.6   |       |

| I <sub>IB</sub>          | Input Bias Current                                                   | 25°C ≤ T <sub>A</sub> ≤ T <sub>A Max</sub>            |        | 10     |              | 10     | μΑ    |

|                          |                                                                      | T <sub>A</sub> = T <sub>A Min</sub>                   |        | 13     |              | 16     |       |

| Ri                       | Input Resistance                                                     | T <sub>A</sub> = 25°C                                 | 6.0    |        | 6.0          |        | kΩ    |

| Cı                       | Input Capacitance <sup>1</sup>                                       | T <sub>A</sub> = 25°C                                 |        | 3.0    |              | 3.0    | pF    |

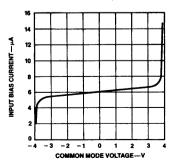

| V <sub>CM</sub>          | Common Mode Voltage Range                                            |                                                       | -3.3   | +3.3   | -3.3         | +3.3   | ٧     |

| CMR                      | Common Mode Rejection                                                | $R_S \le 100 \Omega$ ,<br>-3.3 $\le V_{CM} \le +3.3V$ | 80     |        | 80           | ,      | dB    |

| PSRR                     | Power Supply Rejection Ratio <sup>3</sup>                            | $R_S \le 100 \Omega$ , $\Delta V_S = \pm 5\%$         | 70     |        | 70           |        | dB    |

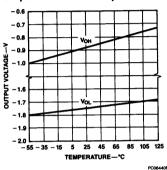

| V <sub>OH</sub>          | Output Voltage HIGH                                                  | T <sub>A</sub> = 25°C                                 | -0.960 | -0.810 | -0.960       | -0.810 | ٧     |

|                          |                                                                      | T <sub>A</sub> = T <sub>A Min</sub>                   | -1.060 | -0.890 | -1.100       | -0.920 |       |

|                          |                                                                      | T <sub>A</sub> = T <sub>A Max</sub>                   | -0.890 | -0.700 | -0.850       | -0.620 |       |

| V <sub>OL</sub>          | Output Voltage LOW                                                   | T <sub>A</sub> = 25°C                                 | -1.850 | -1.650 | -1.850       | -1.650 | ٧     |

|                          |                                                                      | T <sub>A</sub> = T <sub>A Min</sub>                   | -1.890 | -1.675 | -1.910       | -1.690 |       |

|                          |                                                                      | T <sub>A</sub> = T <sub>A Max</sub>                   | -1.825 | -1.625 | -1.810       | -1.575 |       |

| l+                       | Positive Supply Current                                              |                                                       |        | 22     |              | 22     | mA    |

| <b> -</b>                | Negative Supply Current                                              |                                                       |        | 26     |              | 26     | mA    |

| P <sub>c</sub>           | Power Consumption <sup>4</sup>                                       |                                                       |        | 300    |              | 300    | mW    |

## Switching Characteristics $V_{in} = 100 \text{ mV}, V_{OD} = 5.0 \text{ mV}$

|                   | ·                                 |                                            | μ <b>Α685V</b> |      | μ <b>Α685M</b> |      |       |

|-------------------|-----------------------------------|--------------------------------------------|----------------|------|----------------|------|-------|

| Symbol            | Characteristic                    | Condition <sup>2</sup>                     | Min.           | Max. | Min.           | Max. | Units |

| t <sub>PD+</sub>  | Input to Output HIGH <sup>3</sup> | T <sub>A Min</sub> ≤ T <sub>A</sub> ≤ 25°C |                | 6.5  |                | 6.5  | ns    |

|                   |                                   | T <sub>A</sub> = T <sub>A Max</sub>        |                | 9.5  |                | 12   | 1     |

| t <sub>PD</sub> _ | Input to Output LOW <sup>3</sup>  | T <sub>A Min</sub> ≤ T <sub>A</sub> ≤ 25°C |                | 6.5  |                | 6.5  | ns    |

|                   |                                   | T <sub>A</sub> = T <sub>A Max</sub>        |                | 9.5  |                | 12   |       |

## μ**A685** (Cont.) **Electrical Characteristics**

Switching Characteristics  $V_{in} = 100$  mV,  $V_{OD} = 5.0$  mV

| Symbol                                                             |                                     |                                                          | μ <b>Α685V</b>         |      | μ <b>A</b> 685 <b>M</b> |      |      |

|--------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------|------------------------|------|-------------------------|------|------|

|                                                                    | Symbol                              | Characteristic                                           | Condition <sup>2</sup> | Min. | Max.                    | Min. | Max. |

| t <sub>PD +</sub> (E)                                              | Latch Enable to Output HIGH         | T <sub>A Min</sub> ≤ T <sub>A</sub> ≤ 25°C               |                        | 6.5  |                         | 6.5  | ns   |

|                                                                    | Delay <sup>3</sup>                  | T <sub>A</sub> = T <sub>A Max</sub>                      |                        | 9.5  |                         | 12   |      |

| t <sub>PD</sub> _(E) Latch Enable to Output LOW Delay <sup>3</sup> |                                     | T <sub>A Min</sub> ≤ T <sub>A</sub> ≤ 25°C               |                        | 6.5  |                         | 6.5  | ns   |

|                                                                    | T <sub>A</sub> = T <sub>A Max</sub> |                                                          | 9.5                    |      | 12                      |      |      |

| t <sub>S</sub>                                                     | Minimum Set up Time <sup>3</sup>    | T <sub>A Min</sub> ≤ T <sub>A</sub> ≤ 25°C               |                        | 3.0  |                         | 3.0  | ns   |

|                                                                    |                                     | T <sub>A</sub> = T <sub>A Max</sub>                      |                        | 4.0  |                         | 6.0  |      |

| t <sub>h</sub>                                                     | Minimum Hold Time <sup>3</sup>      | T <sub>A Min</sub> ≤ T <sub>A</sub> ≤ T <sub>A Max</sub> |                        | 1.0  |                         | 1.0  | ns   |

| t <sub>pw</sub> (E)                                                | Minimum Latch Enable Pulse          | T <sub>A Min</sub> ≤ T <sub>A</sub> ≤ 25°C               |                        | 3.0  |                         | 3.0  | ns   |

|                                                                    | Width <sup>3</sup>                  | T <sub>A</sub> = T <sub>A Max</sub>                      |                        | 4.0  |                         | 5.0  | 1    |

#### Notes

- 1. For TO-99 only; CERDIP = 7.0 pF.

- 2. Unless otherwise specified V+ = 6.0 V, V- = -5.2 V, V<sub>T</sub> = -2.0 V, and R<sub>L</sub> = 50 Ω; all switching characteristics are for a 100 mV input step with 5.0 mV overdrive. The specifications given for V<sub>IO</sub>, I<sub>IO</sub>, I<sub>IO</sub>, I<sub>IO</sub>, SRR, PSRR, t<sub>PD+</sub> and t<sub>PD-</sub> apply over the full V<sub>CM</sub> range and for ±5% supply voltages. The µA685 is designed to meet the specifications given in the table after thermal equilibrium has been established with a transverse air flow of 500 LFPM or greater.

- 3. Guaranteed, but not tested in production.

- 4. Refer to Internal Power Dissipation in Absolute Maximum Rating Table.

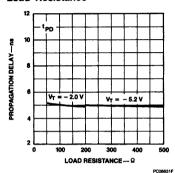

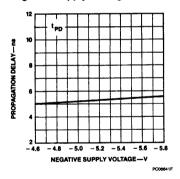

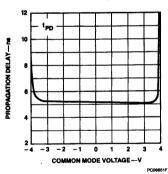

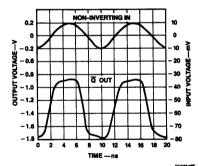

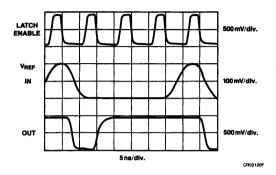

Typical Performance Curves  $T_A = 25^{\circ}C$ , V+ = 6.0 V, V- = -5.2 V,  $V_T = -2.0$  V,  $R_L = 50$   $\Omega$ , and switching characteristics are for  $V_{in} = 100$  mV,  $V_{OD} = 5.0$  mV, unless otherwise specified.

## Response for Various Load Resistances

## Response for Various Load Resistances

Propagation Delay vs Load Resistance

## Propagation Delay vs Negative Supply Voltage

## Propagation Delay vs Common Mode Voltage

## Response to 100 MHz Sine Wave

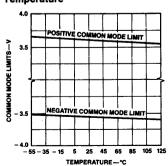

## Common Mode Limits vs Temperature

PC08550F

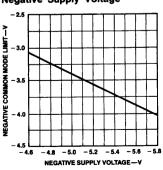

## Negative Common Mode Limit vs Negative Supply Voltage

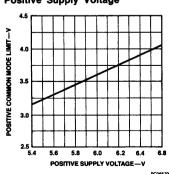

Positive Common Mode Limit vs Positive Supply Voltage

C06570F

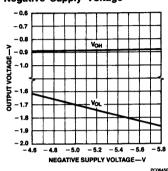

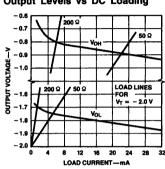

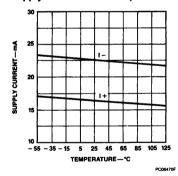

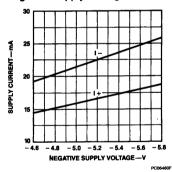

## Typical Performance Curves (Cont.) $T_A = 25$ °C, $V_T = -2.0$ V, $V_T = -2.0$ otherwise specified.

**Output Levels vs Temperature**

**Negative Supply Voltage**

**Output Levels vs**

Output Levels vs DC Loading

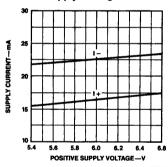

Supply Currents vs Temperature

Supply Currents vs **Negative Supply Voltage**

Supply Currents vs **Positive Supply Voltage**

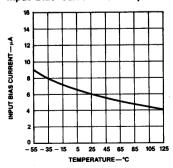

Input Bias Current vs Temperature

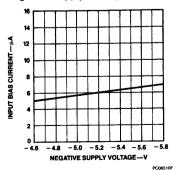

Input Bias Current vs **Negative Supply Voltage**

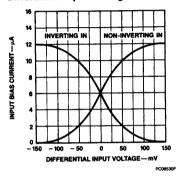

Input Bias Current vs Common Mode Voltage

Typical Performance Curves (Cont.)  $T_A = 25^{\circ}\text{C}$ ,  $V_{+} = 6.0 \text{ V}$ ,  $V_{-} = -5.2 \text{ V}$ ,  $V_{T} = -2.0 \text{ V}$ ,  $R_L = 50 \Omega$ , and switching characteristics are for  $V_{\text{in}} = 100 \text{ mV}$ ,  $V_{\text{OD}} = 5.0 \text{ mV}$ , unless otherwise specified.

## Input Current vs Differential Input Voltage

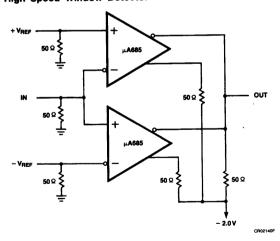

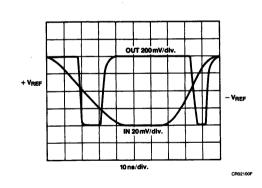

Typical Applications (T<sub>A</sub> = 25°C)

## **High Speed Window Detector**

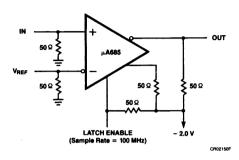

## Typical Applications (Cont.)

## **High Speed Sampling**

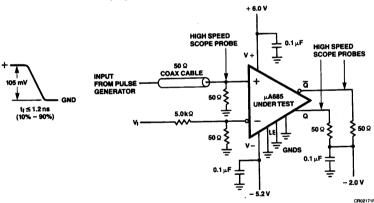

Measurement Of Propagation Delay

Propagation delays  $t_{PD}+(\overline{Q})$  output) and  $t_{PD}-(\overline{Q})$  output) are measured with input signal conditions of a 100 mV step with an overdrive of 5.0 mV (the overdrive is the voltage in excess of that needed to bring the output to the center of its dynamic range). Offset is compensated for by adjusting  $V_1$  until outputs are in the linear region while the Pulse Generator is disconnected.  $V_1$  is then increased in the positive direction so inverting input changes by 5.0 mV, i.e. the overdrive condition. Propagation delays are then measured with actual input pulse condition of +105 mV to 0 V swing, with a  $t_{PD}+$  or  $t_{PD}-$  reading taken between the +5.0 mV level of the input pulse and the 50% point of the outputs.

### Thermal Considerations

To achieve the high speed of the  $\mu$ A685, a certain amount of power must be dissipated as heat. This in-

creases the temperature of the die relative to the ambient temperature. In order to be compatible with ECL III and ECL 10,000, which normally use air flow as a means of package cooling, the  $\mu$ A685 characteristics are specified when the device has an air flow across the package of 500 linear feet per minute or greater. Thus, even though different ECL circuits on a printed circuit board may have different power dissipations, all will have the same input and output levels, etc. provided each sees the same air flow and air temperature. This eases design, since the only change in characteristics between devices is due to the increase in ambient temperature of the air passing over the devices. If the  $\mu$ A685 is operated without air flow, the change in electrical characteristics due to the increased die temperature must be taken into account.

## Interconnection Techniques

All high speed ECL circuits require that special precautions be taken for optimum system performance. The  $\mu$ A685 is particularly critical because it features very high gain (60 dB) at very high frequencies (100 MHz). A ground plane must be provided for a good, low inductance, ground current return path. The impedance at the inputs should be as low as possible and lead lengths as short as practical. It is preferable to solder the device directly to the printed circuit board instead of using a socket. Open wiring on the outputs should be limited to less than one inch, since severe ringing occurs beyond this length. For

longer lengths, the printed circuit interconnections become microstrip transmission lines when backed up by a ground plane, with a characteristic impedance of 50 to 150  $\Omega$ . Reflections will occur unless the line is terminated in its characteristic impedance. The termination resistors normally go to -2.0 V, but a Thevenin equivalent to V- can be used at some increase in power. Best results are usually obtained with the terminating resistor at the end of the driven line. The lower impedance lines are more suitable for driving capacitive loads. The supply voltages should be decoupled with RF capacitors connected to the ground plane as close to the device supply leads as possible.

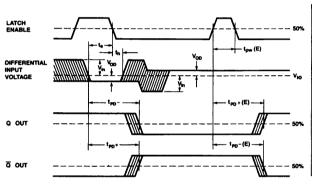

## **Timing Diagram**

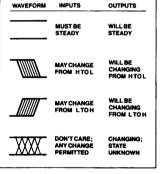

# Key To Timing Diagram WAVEFORM INPUTS OUTPUTS

#### Note

The set up and hold times are a measure of the time required for an input signal to propagate through the first stage of the comparator to reach the latching circuitry. Input signal changes occurring before  $t_s$  will be detected and held; those occurring after  $t_h$  will not be detected. Changes between  $t_s$  and  $t_h$  may or may not be detected.

#### **Definition Of Terms**

V<sub>IO</sub> Input Offset Voltage — That voltage which must be applied between the two input terminals through two equal resistances to obtain zero voltage between the two outputs.

Input Offset Current — The difference between the currents into the two input terminals when there is zero voltage between the two outputs.

I<sub>IB</sub> Input Bias Current — The average of the two input currents.

Input Resistance — The resistance looking into either input terminal with the other grounded.

Input Capacitance — The capacitance looking into either input terminal with the other grounded.

V<sub>CM</sub> Common Mode Voltage Range — The range of voltages on the input terminals for which the offset and propagation delay specifications apply.

CMR Common Mode Rejection — The ratio of the input voltage range to the peak-to-peak change in input offset voltage over this range.

Power Supply Rejection Ratio — The ratio of the change in input offset voltage to the change in power supply voltages producing it.

Output Voltage HIGH — The logic HIGH output voltage with an external pull-down resistor returned to a negative supply.

Rı

Cı

**PSRR**

VOH

- V<sub>OL</sub> Output Voltage LOW The logic LOW output voltage with an external pull-down resistor returned to a negative supply.

- I+ Positive Supply Current The current required from the positive supply to operate the comparator.

- Negative Supply Current The current required from the negative supply to operate the comparator.

- P<sub>c</sub> Power Consumption The power dissipated by the comparator with both outputs terminated in 50  $\Omega$  to -2.0 V.

## Switching Terms (see Timing Diagram)

- tpp+ Input To Output HIGH Delay The propagation delay measured from the time the input signal crosses the input offset voltage to the 50% point of an output LOW to HIGH transition.

- t<sub>PD</sub>— Input To Output LOW Delay The propagation delay measured from the time the input signal crosses the input offset voltage to the 50% point of an output HIGH to LOW transition.

- t<sub>PD+(E)</sub> Latch Enable To Output HIGH Delay The propagation delay measured from the 50% point of the Latch Enable signal LOW to HIGH transition to the 50% point of an output LOW to HIGH transition.

- tpD-(E)

Latch Enable To Output LOW Delay The propagation delay measured from the 50% point of the Latch Enable signal HIGH to LOW transition to the 50% point of an output HIGH to LOW transition.

- ts Minimum Set up Time The minimum time before the negative transition of the Latch Enable signal that an input signal change must be present in order to be acquired and held at the outputs.

- th Minimum Hold Time The minimum time after the negative transition of the Latch Enable signal that the input signal must remain unchanged in order to be acquired and held at the outputs.

- tpw(E) Minimum Latch Enable Pulse Width The minimum time that the Latch Enable signal must be HIGH in order to acquire and hold an input signal change.

## Other Symbols

| • | TA | Ambient temperature                        | V <sub>T</sub> | Output load terminating voltage                 |

|---|----|--------------------------------------------|----------------|-------------------------------------------------|

|   | •  | Input source resistance<br>Supply voltages | _              | Output load resistance<br>Input pulse amplitude |

|   |    |                                            |                | Input overdrive                                 |

| 1 | V- | Negative supply voltage                    | f              | Frequency                                       |